# Tesis doctoral Soporte de Reducciones y Orden en Sistemas de Memoria Transaccional

# Manuel Pedrero Luque

Dirigida por Eladio D. Gutiérrez Carrasco y Óscar Plata González

AUTOR: Manuel Pedrero Luque

iD http://orcid.org/0000-0003-3062-4204

EDITA: Publicaciones y Divulgación Científica. Universidad de Málaga

Esta obra está bajo una licencia de Creative Commons Reconocimiento-NoComercial-SinObraDerivada 4.0 Internacional:

http://creativecommons.org/licenses/by-nc-nd/4.0/legalcode

Cualquier parte de esta obra se puede reproducir sin autorización

pero con el reconocimiento y atribución de los autores.

No se puede hacer uso comercial de la obra y no se puede alterar, transformar o hacer obras derivadas.

Esta Tesis Doctoral está depositada en el Repositorio Institucional de la Universidad de Málaga (RIUMA): riuma.uma.es

### Departamento de Arquitectura de Computadores

#### **TESIS DOCTORAL**

# Soporte de Reducciones y Orden en Sistemas de Memoria Transaccional

Manuel Pedrero Luque Noviembre de 2018

Dirigida por Dr. Eladio Gutiérrez Carrasco Dr. Óscar Plata González

Dr. D. Eladio D. Gutiérrez Carrasco. Profesor Titular del Departamento de Arquitectura de Computadores. Universidad de Málaga.

Dr. D. Óscar Plata González. Catedrático del Departamento de Arquitectura de Computadores. Universidad de Málaga.

#### **CERTIFICAN:**

Que la memoria titulada "Soporte de Reducciones y Orden en Sistemas de Memoria Transaccional" ha sido realizada por D. Manuel Pedrero Luque bajo nuestra dirección en el Departamento de Arquitectura de Computadores de la Universidad de Málaga, y constituye la Tesis que presenta para optar al grado de Doctor en Ingeniería Informática.

Málaga, noviembre de 2018

Dr. D. Eladio D. Gutiérrez Carrasco. Codirector de la tesis.

Dr. D. Óscar Plata González. Tutor y codirector de la tesis.

### A mi familia

# Agradecimientos

Durante los últimos años he tenido el placer de convivir con multitud de personas que, directa o indirectamente, han sido partícipes de este trabajo. Sirvan estas líneas como reconocimiento a todas ellas.

En primer lugar quiero dar las gracias a mis directores Oscar Plata y Eladio Gutiérrez por su acogida en el grupo de investigación y por su confianza y apoyo durante estos años. Si esta tesis ha llegado a buen puerto es sin duda gracias a ellos, a su disponibilidad, su dedicación, su consejo y su ayuda. Quiero agradecer igualmente a Ezequiel Herruzo, de la Universidad de Córdoba, su recomendación para entrar a formar parte de este equipo y a Sergio Romero su ayuda y apoyo en varias de las contribuciones de esta tesis.

Reitero mi agradecimiento a Oscar por darme además la oportunidad de impartir docencia durante este periodo, así como a los profesores Julián, Francisco, Gerardo, Luis Felipe y Julio, con los que he tenido el privilegio de trabajar, sin olvidar al resto de profesores del departamento, siempre disponibles para echarme una mano. Gracias por vuestra confianza y vuestro consejo.

Del mismo modo, me gustaría extender mi agradecimiento al resto del departamento de Arquitectura de Computadores de la Universidad de Málaga; muy especialmente a los técnicos, Paco, Juanjo y Mª Carmen y a la secretaria, Carmen. Gracias por vuestra disponibilidad y vuestra ayuda.

Finalmente no puedo dejar de agradecer a mis compañeros de laboratorio y de fatigas su acogida, su apoyo y el gran ambiente de trabajo que me he encontrado desde el primer día: Mángel, Ricardo, Cervilla, Alberto, Pirlo, Sergio, Carlos, Villegas, Vilches, Upton, Arjona, Fran, Lázaro, Serrucho, Denisa, Andrés, Bernabé, José Carlos, Iván y aquellos a los que haya podido olvidar. Gracias a todos.

Debo mencionar además las fuentes de financiación que me han permitido llevar a cabo las investigaciones que han dado lugar a esta tesis: los proyectos TIN2013-42253-P y TIN2016-80920-R del Gobierno de España, el proyecto P12-TIC-1470 de la Junta de Andalucía y el plan propio de la Universidad de Málaga.

## Resumen

La popularización de los chips multiprocesador ha supuesto un cambio profundo en la comunidad de desarrollo software. La programación secuencial tradicional no permite aprovechar al máximo los recursos hardware disponibles en los procesadores actuales, mientras que la programación paralela eficiente es una tarea compleja que requiere de conocimientos detallados sobre la arquitectura del procesador, así como de nuevos algoritmos y herramientas.

El paradigma de Memoria Transaccional (TM) ha surgido como una alternativa a los modelos basados en *locks* para la programación paralela convencional basada en exclusión mutua, con la promesa de facilitar el desarrollo de programas multihilo siguiendo un modelo de concurrencia optimista. Los sistemas TM se basan en el concepto de *transacción*; un bloque de instrucciones que se ejecuta en paralelo manteniendo la consistencia con el resto de código y propagando los cambios de forma atómica al resto de hilos concurrentes. El sistema TM es responsable de detectar y resolver posibles conflictos entre las transacciones para mantener estas propiedades de manera transparente al programador. Dado que la resolución de un conflicto implica normalmente el aborto de alguna de las transacciones implicadas, el volumen de estos conflictos es un aspecto crítico que condiciona en buena medida el rendimiento final de la aplicación. Los sistemas TM pueden implementarse mediante librerías software (STM) o ser soportarlos directamente en el hardware del procesador (HTM).

En esta tesis se proponen soluciones basadas en memoria transaccional para optimizar la detección y resolución de conflictos en códigos que presentan operaciones de reducción. Las reducciones aparecen frecuentemente en aplicaciones científicas en combinación con patrones de acceso irregulares que dificultan en gran medida su paralelización de forma eficiente. Nuestra propuesta contempla las reducciones como una operación transaccional adicional en el modelo TM. A diferencia de un sistema TM tradicional, el tratamiento explícito de las reduccio-

nes permite filtrar los conflictos originados por dichas operaciones manteniendo la consistencia del sistema sin necesidad de abortar transacciones.

Este trabajo introduce además un orden total de precedencia entre transacciones que implica que éstas confirmen sus cambios a memoria en un orden específico, facilitando así la paralelización de aplicaciones secuenciales. El uso de este orden permite además detectar *reducciones parciales*; accesos a memoria que violan las condiciones de reducción. El sistema TM utiliza la información de precedencia para resolver otros conflictos entre transacciones sin producir abortos. Esta propuesta se evalúa comparándola con otros métodos utilizados tradicionalmente para paralelizar códigos con operaciones de reducción, incluyendo el uso de *locks* de grano grueso y de grano fino, privatización y el uso de un TM clásico con restricciones de orden.

Dado que un orden de precedencia estricto penaliza el rendimiento y puede ser demasiado restrictivo en muchos algoritmos, esta tesis aborda también el diseño de un orden de precedencia parcial, donde las restricciones a la hora de confirmar los cambios a memoria no se aplican entre transacciones individuales sino entre grupos de ellas. Este modelo permite aumentar el grado de paralelismo de la aplicación, eliminando restricciones a la hora de confirmar los cambios entre transacciones de un mismo grupo y mejorando así el rendimiento. Con el objetivo de proporcionar una interfaz familiar al programador, introducimos el concepto de barrera transaccional, una primitiva cuya semántica es similar a una barrera de sincronización tradicional, pero que aprovecha TM para permitir a los hilos seguir ejecutando código de forma especulativa. Nuestra propuesta utiliza estas barreras para establecer un orden parcial de precedencia, lanzando transacciones con restricciones de precedencia dinámicas que permiten evitar bloqueos debidos a la sincronización y mantener a la vez la corrección del programa. En este caso, los escenarios de interés son códigos que utilizan barreras para sincronizar diferentes hilos de ejecución.

Los experimentos de esta tesis se han llevado a cabo sobre sistemas reales. Los modelos STM con soporte de reducciones se han implementado como una librería accesible por las aplicaciones paralelas mediante una API similar a la utilizada en otros STM. Por su parte, los modelos HTM se han implementado sobre las extensiones transaccionales del procesador POWER8, aprovechando la posibilidad que brinda de ejecutar instrucciones no transaccionales en el contexto de una transacción. Para ello hemos instrumentado las llamadas a las instrucciones de inicio y fin de transacción aprovechando el soporte transaccional existente.

Resumen

La evaluación se ha llevado a cabo utilizando una selección de *benchmarks* reales y sintéticos que incluye la suite STAMP, específicamente diseñada para evaluar sistemas TM; Eigenbench, que permite analizar ortogonalmente características de los sistemas TM; códigos seleccionados de las suites SPEC, PARSEC, y Polybench; y otros kernels de aplicaciones HPC de interés.

# Índice general

| Αę | grade          | cimientos                                                 | 1    |  |  |

|----|----------------|-----------------------------------------------------------|------|--|--|

| Re | esume          | en                                                        | Ш    |  |  |

| Ín | Índice general |                                                           |      |  |  |

| Ín | dice (         | de figuras                                                | XIII |  |  |

| Ín | dice (         | de tablas                                                 | XVII |  |  |

| 1. | Intr           | oducción                                                  | 1    |  |  |

|    | 1.1.           | La complejidad de la programación paralela                | 3    |  |  |

|    | 1.2.           | Memoria transaccional                                     | 5    |  |  |

|    |                | 1.2.1. Ventajas de la memoria transaccional               | 6    |  |  |

|    |                | 1.2.2. Técnicas de especulación con soporte transaccional | 7    |  |  |

|    |                | 1.2.3. Operaciones de reducción y memoria transaccional   | 8    |  |  |

|    | 1.3.           | Motivación y contribuciones                               | 8    |  |  |

|    | 1.4.           | Estructura de la tesis                                    | 11   |  |  |

| 2. | Ant            | ecedentes                                                 | 13   |  |  |

|    | 2.1.           | Transacciones                                             | 13   |  |  |

|    | 2.2.           | La interfaz transaccional                                 | 15   |  |  |

| El esp | acio de diseño en memoria transaccional                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3.1. | Control de concurrencia                                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3.2. | Gestión de versiones                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3.3. | Detección de conflictos                                         | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Semár  | ntica transaccional                                             | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4.1. | Atomicidad                                                      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4.2. | Criterios de consistencia                                       | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Historias y ejecuciones                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Criterios de consistencia                                       | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4.3. | Transacciones anidadas                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4.4. | Restricciones de orden                                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Sistem | nas de memoria transaccional                                    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5.1. | Sistemas TM software                                            | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Transactional Mutex Locks                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Transactional Locking II                                        | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | TinySTM                                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | NOrec                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | InvalSTM                                                        | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5.2. | Sistemas TM hardware                                            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Herlihy HTM                                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Virtualized Transactional Memory                                | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | LogTM                                                           | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Transactional Coherence and Consistency                         | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | Intel Transactional Syncronization Extensions                   | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | IBM Blue Gene/Q                                                 | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | IBM System Z                                                    | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | IBM POWER8                                                      | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5.3. | Sistemas TM híbridos                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | 2.3.1. 2.3.2. 2.3.3. Semár 2.4.1. 2.4.2.  2.4.3. 2.5.1.  2.5.1. | 2.3.2. Gestión de versiones 2.3.3. Detección de conflictos Semántica transaccional 2.4.1. Atomicidad 2.4.2. Criterios de consistencia Historias y ejecuciones Criterios de consistencia 2.4.3. Transacciones anidadas 2.4.4. Restricciones de orden Sistemas de memoria transaccional 2.5.1. Sistemas TM software Transactional Mutex Locks Transactional Locking II TinySTM NOrec InvalSTM 2.5.2. Sistemas TM hardware Herlihy HTM Virtualized Transactional Memory LogTM Transactional Coherence and Consistency Intel Transactional Syncronization Extensions IBM Blue Gene/Q IBM System Z IBM POWER8 |

51

52

53

54

|    |      |         | •                                                               |     |

|----|------|---------|-----------------------------------------------------------------|-----|

| 3. | Sop  | orte de | reducciones y orden en memoria transaccional software           | 57  |

|    | 3.1. | Aplica  | ciones irregulares                                              | 57  |

|    | 3.2. | Patron  | es de reducción                                                 | 59  |

|    |      |         | Reducciones parciales                                           | 60  |

|    |      | 3.2.1.  | Técnicas clásicas para la paralelización de reducciones         | 63  |

|    |      |         | Técnicas basadas en exclusión mutua                             | 63  |

|    |      |         | Técnicas basadas en privatización                               | 64  |

|    |      |         | Técnicas basadas en el particionado del espacio de reducción    | 65  |

|    |      | 3.2.2.  | Paralelización de reducciones con soporte TM $ \ldots  \ldots $ | 65  |

|    | 3.3. | Redux   | STM                                                             | 68  |

|    |      | 3.3.1.  | Características                                                 | 68  |

|    |      | 3.3.2.  | Diseño                                                          | 74  |

|    |      |         | ReduxSTM-TS                                                     | 77  |

|    |      |         | ReduxSTM-CTI                                                    | 82  |

|    |      | 3.3.3.  | Implementación                                                  | 88  |

|    |      |         | Mecanismos de sincronización                                    | 88  |

|    |      |         | Barreras de memoria                                             | 89  |

|    |      |         | Estructuras de datos para búferes de escritura y reducción      | 92  |

|    |      |         | Estructuras de datos para timestamps (ReduxSTM-TS)              | 95  |

|    |      |         | Estructuras para los conjuntos de datos (ReduxSTM-CTI) .        | 96  |

|    |      |         | Criterios de corrección: Opacidad y VWC                         | 97  |

|    |      |         | Optimizaciones adicionales                                      | 104 |

HyTM .....

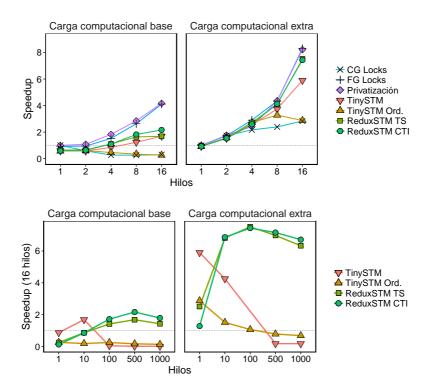

|    |      |         | Eigenbench                                        | 115 |

|----|------|---------|---------------------------------------------------|-----|

|    |      |         | Wormbench                                         | 117 |

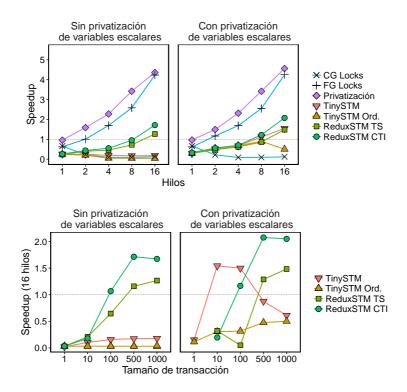

|    |      | 3.4.2.  | Reducciones irregulares                           | 120 |

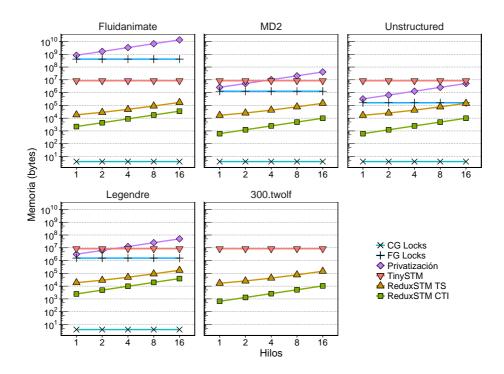

|    |      |         | FluidAnimate                                      | 121 |

|    |      |         | MD2                                               | 124 |

|    |      |         | Euler                                             | 124 |

|    |      |         | Legendre                                          | 125 |

|    |      |         | Requerimientos de memoria                         | 126 |

|    |      | 3.4.3.  | Reducciones Parciales                             | 129 |

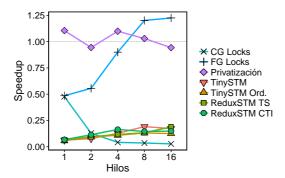

|    |      |         | TWolf                                             | 129 |

|    |      | 3.4.4.  | Códigos generales                                 | 130 |

|    |      |         | STAMP                                             | 131 |

|    |      | 3.4.5.  | Soporte para técnicas de especulación             | 133 |

|    |      |         | SPEC2006                                          | 135 |

|    | 3.5. | Trabaj  | os relacionados                                   | 138 |

|    | 3.6. | Concl   | usiones                                           | 141 |

| 4. | Sope | orte de | orden parcial en memoria transaccional hardware   | 143 |

|    | 4.1. | Introd  | ucción                                            | 143 |

|    | 4.2. | Limita  | aciones de los HTM comerciales                    | 146 |

|    |      |         | Comunicación entre transacciones y suspended mode | 147 |

|    |      | 4.2.1.  | Garantías de progreso en HTM best-effort          | 148 |

|    | 4.3. | Barrer  | as Transaccionales                                | 150 |

|    |      |         | Reemplazando barreras con transacciones ordenadas | 152 |

|    |      |         | TMbarrier                                         | 152 |

|    |      | 4.3.1.  | Restricciones de orden                            | 154 |

RXasRW (Reductions as Read+Write) . . . . . . . . . . . . . . . . . 108

|         | 4.3.2.  | Transacciones anidadas                         | 155 |

|---------|---------|------------------------------------------------|-----|

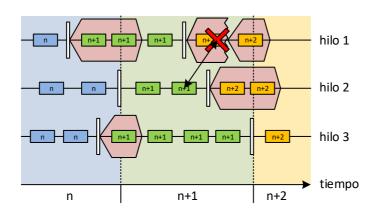

|         | 4.3.3.  | Funcionamiento de TMbarrier                    | 155 |

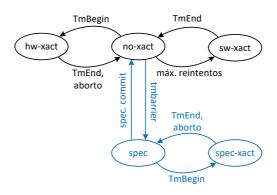

| 4.4.    | Diseño  | o de TMbarrier                                 | 156 |

|         | 4.4.1.  | Nuevos estados en los hilos de ejecución       | 157 |

|         | 4.4.2.  | La primitiva tmbarrier                         | 159 |

|         | 4.4.3.  | Iniciando transacciones                        | 159 |

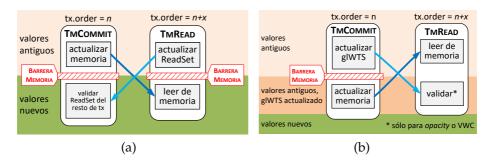

|         | 4.4.4.  | Finalizando transacciones                      | 160 |

|         | 4.4.5.  | Gestionando las limitaciones del HTM de POWER8 | 162 |

|         |         | Granularidad de la detección de conflictos     | 162 |

|         |         | Interacciones en suspended mode                | 163 |

|         |         | Limitaciones del anidamiento de transacciones  | 164 |

|         |         | Política de resolución de conflictos           | 165 |

| 4.5.    | Evalua  | ación                                          | 165 |

|         | 4.5.1.  | Microbenchmark sintético                       | 167 |

|         | 4.5.2.  | Livermore Loop 6: Recurrencia Lineal           | 170 |

|         | 4.5.3.  | Algoritmo CFL                                  | 174 |

| 4.6.    | Trabaj  | os relacionados                                | 179 |

| 4.7.    | Conclu  | usiones                                        | 180 |

| 5. Cor  | clusion | ies y trabajos futuros                         | 183 |

| 5.1.    | Concl   | usiones                                        | 184 |

| 5.2.    | Trabaj  | os futuros                                     | 187 |

| A. API  | transac | ccional y simulación de trazas                 | 189 |

| A.1.    | Una in  | nterfaz transaccional unificada                | 189 |

| A.2.    | Simula  | ación de trazas                                | 191 |

| Bibliog | grafía  |                                                | 195 |

|         |         |                                                |     |

# Índice de figuras

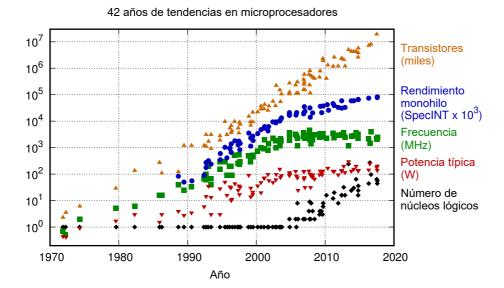

| 1.1. | Evolución de los procesadores desde 1970              | 2  |

|------|-------------------------------------------------------|----|

| 2.1. | Interfaz transaccional mínima                         | 15 |

| 2.2. | Control de concurrencia                               | 16 |

| 2.3. | Diferencias entre <i>locks</i> y transacciones        | 21 |

| 2.4. | Diferencias entre aislamiento fuerte y débil          | 22 |

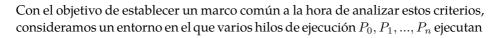

| 2.5. | Ejemplo de historias y ejecuciones                    | 25 |

| 2.6. | Límites de serializability                            | 27 |

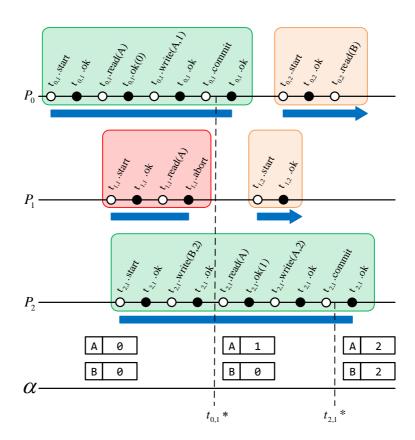

| 2.7. | Criterios de consistencia en un sistema transaccional | 29 |

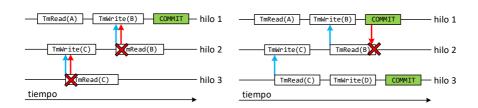

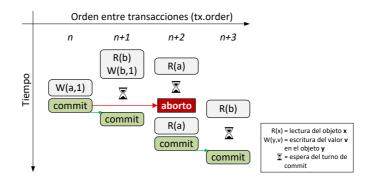

| 2.8. | Ejemplo del uso de orden en transacciones             | 31 |

| 2.9. | Mejoras de TinySTM respecto a TL-2                    | 38 |

| 3.1. | Ejemplos de bucles de reducción                       | 60 |

| 3.2. | Kernels reales con bucles de reducción                | 61 |

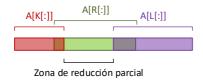

| 3.3. | Ejemplos de reducciones parciales                     | 62 |

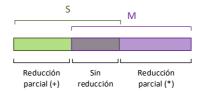

| 3.4. | Paralelización de bucles de reducción utilizando TM   | 67 |

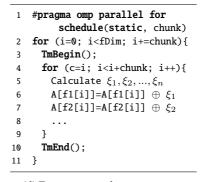

| 3.5. | Bucles de reducción irregulares                       | 69 |

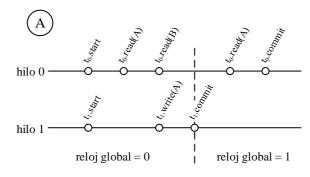

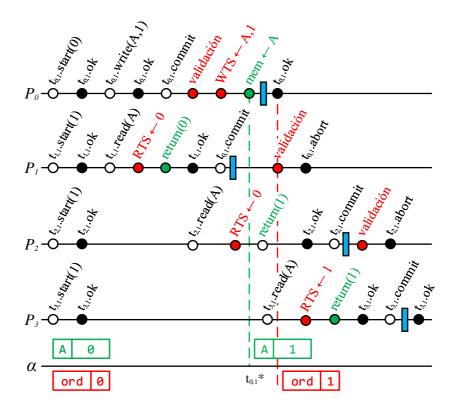

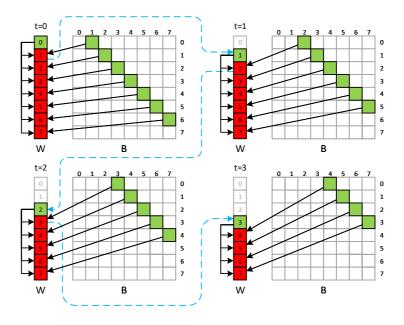

| 3.6. | Funcionamiento de ReduxSTM-TS                         | 78 |

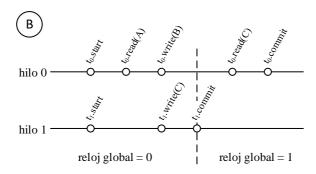

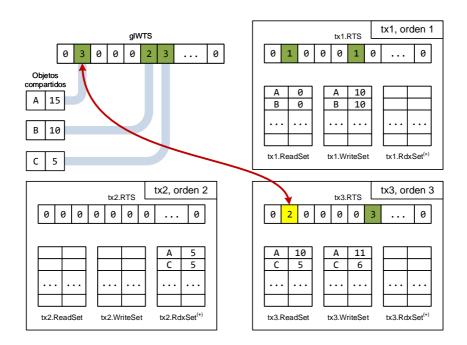

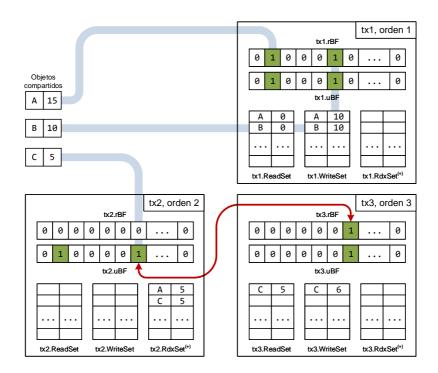

| 3.7. | Funcionamiento de ReduxSTM-CTI                        | 84 |

| 3.8. | Sincronización en ReduxSTM: commits ordenados         | 88 |

| 3.9. Sincronización en ReduxSTM-CTI                                      | 90 |

|--------------------------------------------------------------------------|----|

| 3.10. Sincronización en ReduxSTM: barreras de memoria                    | 91 |

| 3.11. Sincronización en ReduxSTM-TS                                      | 93 |

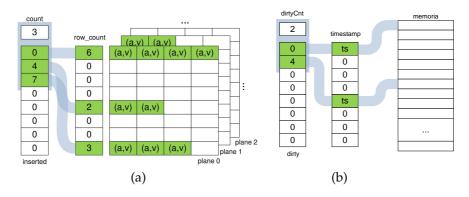

| 3.12. ReduxSTM: estructuras de datos                                     | 95 |

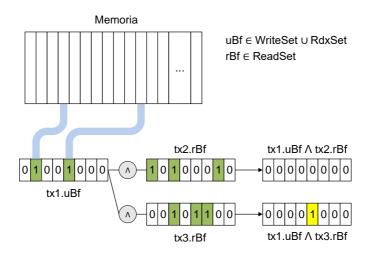

| 3.13. ReduxSTM-CTI: filtros de Bloom                                     | 96 |

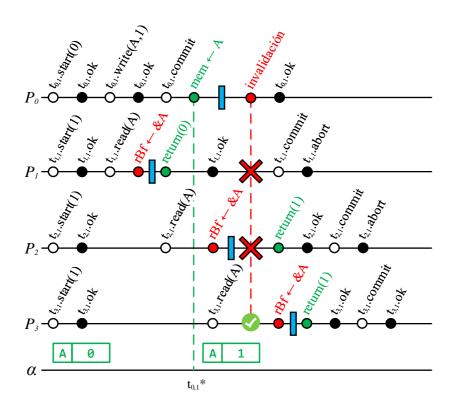

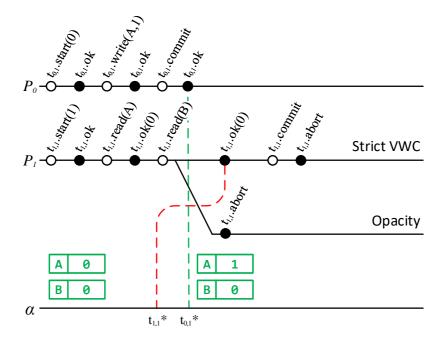

| 3.14. Opacity y VWC en ReduxSTM                                          | 99 |

| 3.15. Extracto del <i>benchmark RXasRW</i>                               | 09 |

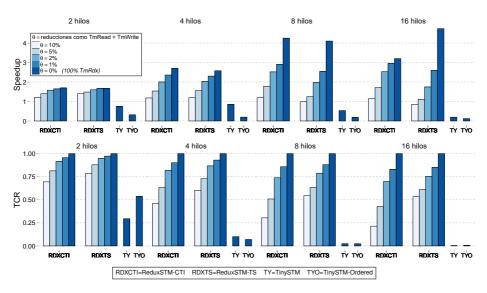

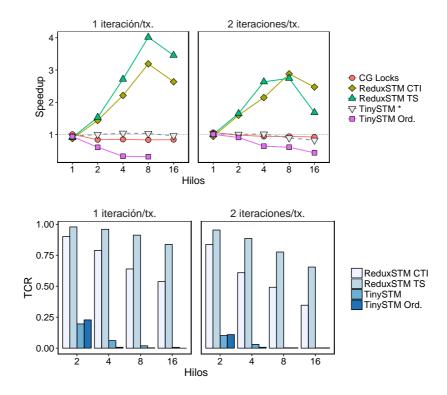

| 3.16. RXasRW: rendimiento y TCR                                          | 10 |

| 3.17. RXasRW: análisis de sensibilidad I                                 | 12 |

| 3.18. RXasRW: análisis de sensibilidad II                                | 14 |

| 3.19. Extracto del <i>kernel</i> de Eigenbench                           | 15 |

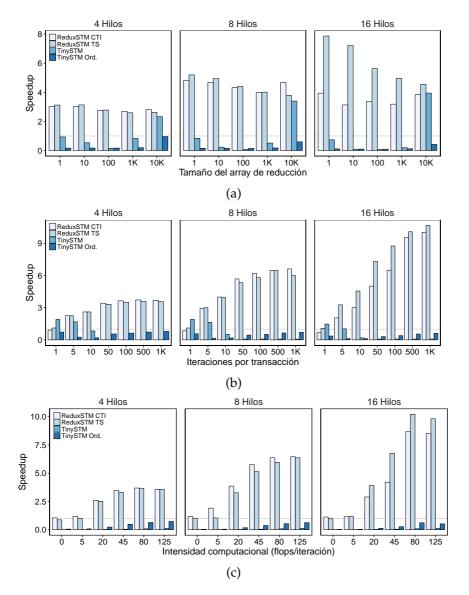

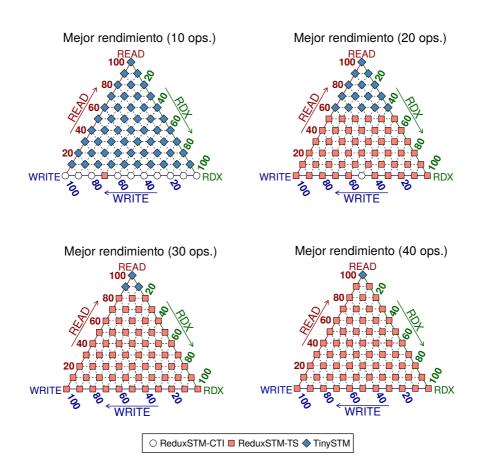

| 3.20. Eigenbench: análisis de rendimiento                                | 17 |

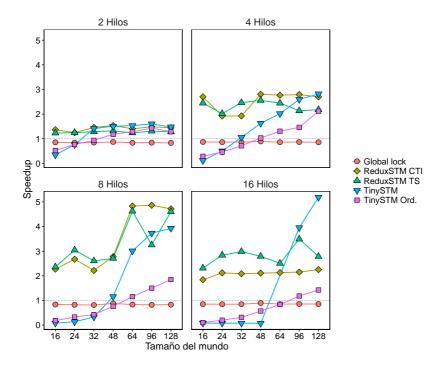

| 3.21. Wormbench: sensibilidad al tamaño del mundo                        | 18 |

| 3.22. Wormbench: <i>speedup</i> relativo                                 | 19 |

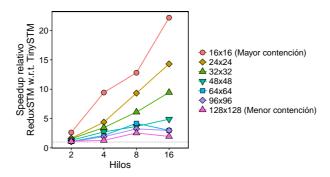

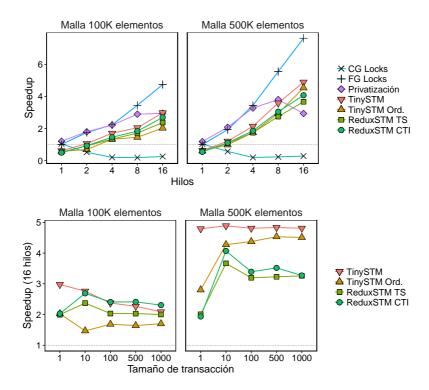

| 3.23. FluidAnimate: rendimiento y sensibilidad al tamaño de transacción1 | 22 |

| 3.24. MD2: rendimiento y sensibilidad al tamaño de transacción 1         | 23 |

| 3.25. Euler: rendimiento y sensibilidad al tamaño de transacción $1$     | 25 |

| 3.26. Legendre: rendimiento                                              | 26 |

| 3.27. Uso de memoria de las diferentes técnicas de paralelización 1      | 27 |

| 3.28. 300.twolf: rendimiento y TCR                                       | 31 |

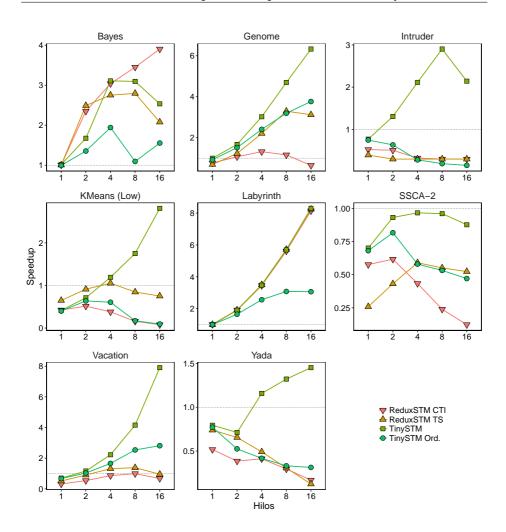

| 3.29. STAMP: comparativa de rendimiento                                  | 34 |

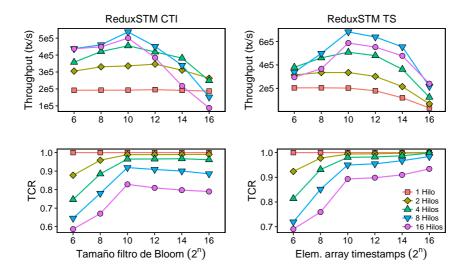

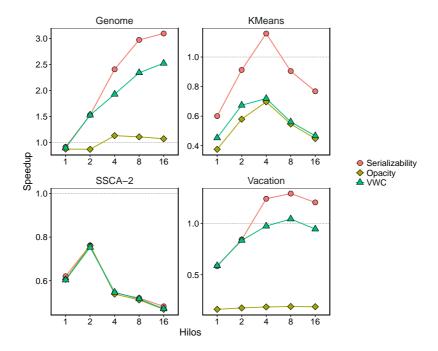

| 3.30. ReduxSTM-TS: influencia del criterio de consistencia               | 35 |

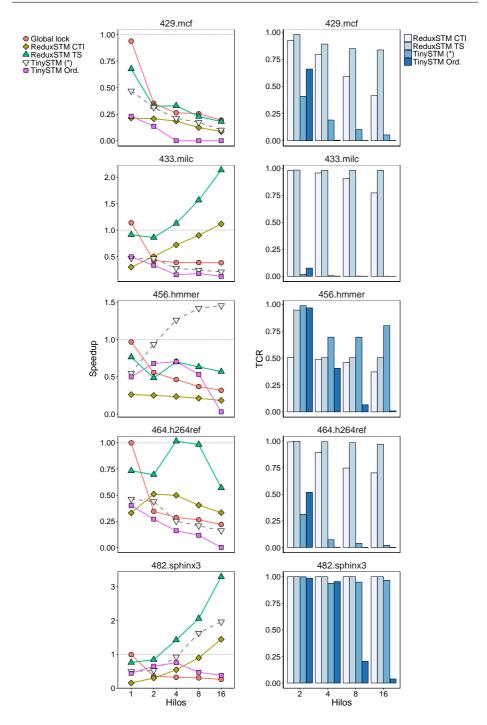

| 3.31. SPEC CPU2006: rendimiento y TCR                                    | 37 |

| 4.1. Dependencias en Livermore Loop 6                                    | 51 |

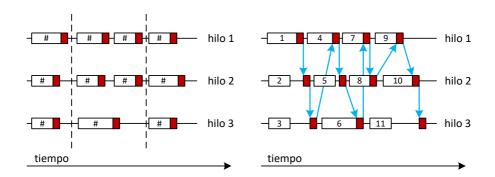

| 4.2. Reemplazando barreras mediante TM con restricciones de orden 1      | 53 |

| 4.3. Funcionamiento de TMbarrier                                         | 56 |

| 4.4. TMbarrier: grafo de estados                                         | 57 |

| 4.5. | Kernel del microbenchmark sintético       | 167 |

|------|-------------------------------------------|-----|

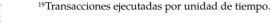

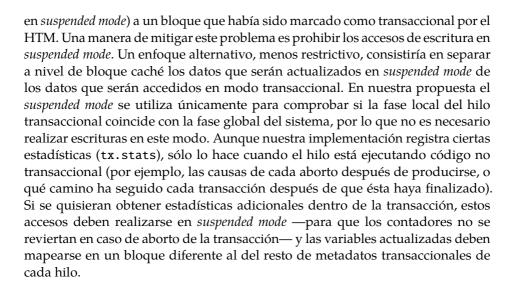

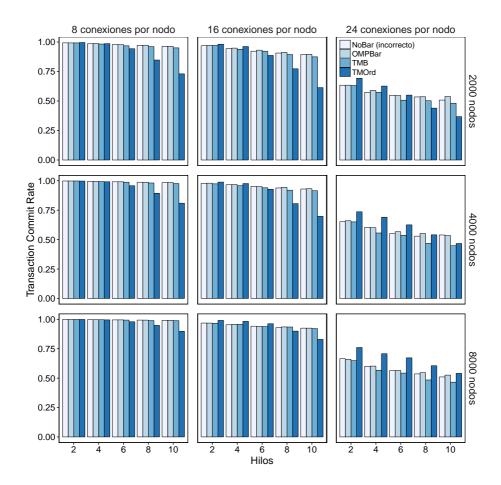

| 4.6. | Microbenchmark: eficiencia y especulación | 168 |

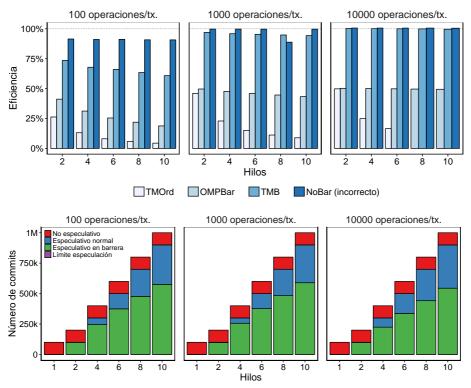

| 4.7. | Recurrence: speedup y TCR                 | 171 |

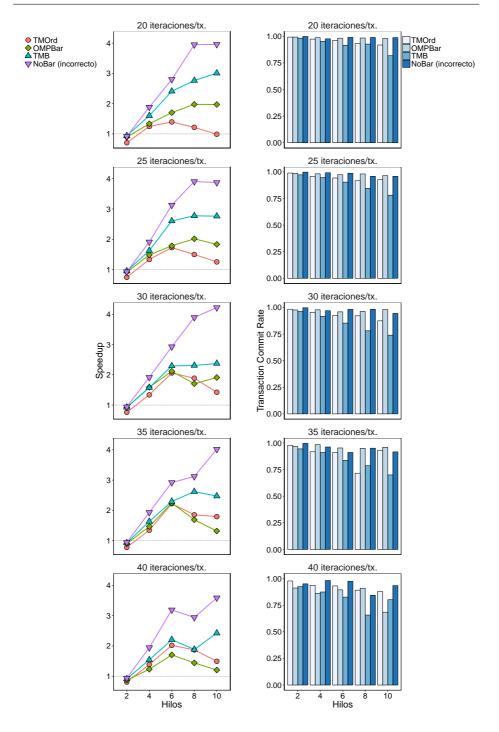

| 4.8. | Speedup algoritmo CFL                     | 176 |

| 4.9. | TCR algoritmo CFL                         | 177 |

|      |                                           |     |

| A.1. | Ejemplo del uso de la API de STAMP        | 192 |

| A.2. | Ejemplo de traza de ejecución             | 193 |

|      |                                           |     |

|      |                                           |     |

# Índice de tablas

| 2.1. | Diferencias entre criterios de consistencia TM                      | 29  |

|------|---------------------------------------------------------------------|-----|

| 2.2. | Resumen de propuestas STM analizadas                                | 34  |

| 2.3. | Resumen de propuestas HTM analizadas                                | 50  |

|      |                                                                     |     |

| 3.1. | Técnicas de paralelización de reducciones                           | 66  |

| 3.2. | Conflictos entre transacciones en diseños STM                       | 73  |

| 3.3. | Notación utilizada en la descripción de los algoritmos de ReduxSTM  | 76  |

| 3.4. | Plataforma de evaluación de ReduxSTM                                | 105 |

| 3.5. | Resumen de los <i>benchmarks</i> utilizados en la evaluación        | 107 |

| 3.6. | Códigos con reducciones irregulares                                 | 120 |

| 3.7. | STAMP: características de las aplicaciones de la suite              | 132 |

| 3.8. | Selección de bucles de la suite SPEC CPU2006                        | 136 |

|      |                                                                     |     |

| 4.1. | Notación utilizada en la descripción de los algoritmos de TMbarrier | 149 |

| 4.2. | Operaciones sobre metadatos en TMbarrier                            | 162 |

| 4.3. | Plataforma de evaluación de TMbarrier                               | 166 |

|      |                                                                     |     |

| A.1. | Primitivas básicas de la API transaccional de STAMP                 | 190 |

| A 2  | Primitivas añadidas a la API transaccional de STAMP                 | 191 |

# Capítulo 1

## Introducción

Durante décadas, el rendimiento de los procesadores ha aumentado de forma sostenida. Dos observaciones empíricas han descrito de este fenómeno. Moore predijo en 1965 un crecimiento exponencial del número de transistores que podía alojar un chip manteniendo el coste [75]. En 1974, Dennard observó que la densidad de potencia de los chips se mantenía constante al reducir el tamaño de los transistores, debido a que también se reducían sus requerimientos de voltaje y corriente [25]. Sin embargo cabe preguntarse, ¿cómo se traducen estas observaciones en el aumento de rendimiento que han experimentado los procesadores durante este tiempo? ¿Por qué se suele relacionar este aumento con la llamada ley de Moore?

Los avances de la tecnología de integración han conseguido disminuir progresivamente el tamaño de los transistores, permitiendo alojar un número cada vez mayor en un mismo chip, y correlándose así con las predicciones de Moore. Por su parte un transistor más pequeño puede cambiar de estado más rápidamente, permitiendo aumentar su frecuencia de funcionamiento. De acuerdo con Dennard, debería consumir también menos energía, permitiendo que el procesador resultante pueda emplear un mayor número de transistores, a mayor frecuencia, todo ello manteniendo el consumo. Esto, unido a la capacidad de los arquitectos de computadores para aprovechar los nuevos transistores disponibles provocó que se relacionase naturalmente la ley de Moore con el rendimiento de los procesadores.

Desde mediados de la pasada década, sin embargo, la frecuencia de funcionamiento de los procesadores se estancó alrededor de los 4GHz, límite que, como

Figura 1.1: Evolución de los procesadores desde 1970. Gráfica adaptada de original de K. Rupp. Los datos hasta 2010 han sido extraídos por M. Horowitz, F. Labonte, O. Shacham, K. Olukotun y C. Batten. Los datos hasta 2017 han sido recopilados por K. Rupp [97].

se observa en la figura 1.1, permanece vigente en la actualidad. La razón no es tanto que la frecuencia no pueda seguir aumentando, sino la energía necesaria para ello. Las observaciones de Dennard dejaron de cumplirse hace años, ya que las corrientes de fuga y el voltaje mínimo de los transistores marcan un límite inferior a su consumo que no escala con el tamaño de los mismos. Conforme los transistores se hacen más pequeños, la densidad energética del procesador aumenta. A mediados de la década de los 2000, este aumento no se pudo seguir ignorando y se llegó al denominado power wall que, en la práctica y unido a otros problemas, limitó la frecuencia a la que podían funcionar los procesadores manteniendo un consumo asumible. En los procesadores actuales, de hecho, un porcentaje cada vez mayor del total de transistores debe permanecer inactivo para mantener el consumo del chip controlado. Esta limitación se conoce como dark silicon y es un problema cada vez mayor, ya que impide aprovechar al máximo los transistores disponibles en el procesador para mejorar su rendimiento. Además, el porcentaje de dark silicon aumenta conforme lo hace la densidad energética del procesador, lo que dificulta justificar la creación de nuevos nodos de fabricación desde un punto de vista comercial.

procesadores de consumo, que pasó de aumentar la complejidad de los núcleos e incrementar su frecuencia de funcionamiento a disminuir dicha frecuencia e integrar varios núcleos independientes en un mismo chip. Este cambio obedece a un doble propósito: permite reducir la energía disipada por el procesador y, al mismo tiempo, maximiza el aprovechamiento de los transistores disponibles. La tendencia se ha mantenido hasta el día de hoy, donde la inmensa mayoría de procesadores de propósito general están compuestos de varios núcleos independientes encapsulados en un mismo chip que acceden a una memoria compartida. Esta configuración conforma una arquitectura MIMD¹ conocida como *chip multi*processor o CMP y es en la que nos centramos en esta tesis. Los CMP necesitan además de una red de interconexión que comunique los distintos núcleos de procesamiento con la memoria global, compartida entre todos ellos. Desde el punto de vista de la programación, esta arquitectura presenta la ventaja de poder intercambiar información entre distintos núcleos mediante el uso de un espacio de memoria compartido. Sin embargo los accesos a datos compartidos necesitan de una coordinación para mantener la consistencia del programa.

Consecuentemente al power wall se produjo un cambio en la industria de los

### 1.1. La complejidad de la programación paralela

A diferencia de las mejoras arquitecturales desarrolladas desde los años 70, la disponibilidad de varios núcleos de procesamiento no se traduce automáticamente en un mayor rendimiento. Mientras que avances como la segmentación, la ejecución fuera de orden o la memoria caché son transparentes al programador, el uso de procesadores multinúcleo supone el paso de la responsabilidad de explotar los recursos hardware de la industria al desarrollador. A su vez, interfiere en conceptos tradicionales para manejar la complejidad en el desarrollo de software tales como la abstracción o la composición.

Para ilustrar lo anterior pensemos en una clase account que permita controlar los depósitos en un banco. Dicha clase dispone de dos métodos para retirar o depositar cierta cantidad de dinero. En un modelo secuencial un programador puede implementar un nuevo método transfer(account src, account tgt) que realice una transferencia a partir de dos cuentas usando los métodos para retirar y depositar en los objetos correspondientes. No es necesario conocer los detalles de implementación de los métodos, por lo que la solución resulta trivial. En un entorno paralelo, sin embargo, el mismo problema requiere que el programador conozca los detalles de implementación de los métodos, si son

atómicos, si usan alguna directiva de bloqueo y las interacciones que pueda tener dicha directiva con el resto de la aplicación. Aun si los métodos son atómicos, esto no garantiza que se puedan combinar de forma atómica. La solución en este caso dista de ser sencilla, pudiéndose producir condiciones de carrera o bloqueos debidos a *deadlocks* si no se consideran las posibles interacciones entre hilos. Finalmente, una implementación válida desde el punto de vista de la corrección de los resultados no tiene por qué ser más eficiente que la solución secuencial.

Estos problemas se deben a que el uso del paralelismo en la programación lleva implícito una falta de determinismo en la ejecución de los diferentes hilos que supone una dificultad añadida respecto a la programación secuencial. La ejecución de un hilo puede verse retrasada por interrupciones, fallos de caché o por el propio planificador del sistema operativo. La duración de estos retrasos puede variar en un rango de varios órdenes de magnitud. El programador debe considerar por tanto la totalidad de eventos que puedan ocurrir de forma concurrente y cómo afectan dichos eventos a la corrección del problema a resolver.

Además de una mayor dificultad a la hora de programar, los posibles errores suelen ser más complicados de detectar y de corregir. Las herramientas de análisis, depuración, modelos de programación y entornos disponibles para la programación paralela no están tan desarrollados como los disponibles para la programación secuencial.

Para explotar el paralelismo se suelen considerar dos modelos. El paralelismo de datos efectúa una serie de operaciones sobre un conjunto de datos de forma simultánea. Suele encontrarse en aplicaciones numéricas que operan sobre vectores o matrices, y puede ser explotado implícitamente en algunos lenguajes o incluso directamente por el compilador, pero no está presente un gran porcentaje de problemas. Por su parte el paralelismo de tareas hace referencia a un modelo más general donde la computación se reparte entre varios hilos que se sincronizan entre sí explícitamente por medio de primitivas como locks, semáforos o barreras. Este modelo no establece restricciones al código que ejecuta cada hilo ni a cómo se comunican los hilos entre sí, por lo que es suficientemente general para englobar a toda forma de paralelismo. Es sin embargo más complicado de programar correctamente, ya que su grado de abstracción puede bajar directamente a nivel ISA (Instruction Set Architecture).

#### 1.2. Memoria transaccional

A pesar de las dificultades asociadas a la programación paralela, los sistemas de bases de datos llevan décadas aprovechando los recursos de los sistemas multiprocesador, ejecutando consultas y operaciones en paralelo sin que los programadores hayan tenido que lidiar explícitamente con la complejidad asociada al paralelismo descrita anteriormente.

Estos sistemas se basan en el concepto de transacción. En bases de datos una transacción garantiza que un conjunto de operaciones sobre la base de datos se realizan, desde el punto de vista del programador, como si el proceso que las ejecuta tuviese acceso exclusivo a la misma. A su vez, el sistema gestor de bases de datos puede permitir la ejecución simultánea de otras operaciones, pero controla y limita las interacciones entre ellas para mantener la consistencia del sistema, garantizando que el resultado final sea indistinguible del que se produciría si todas las operaciones se ejecutasen de forma secuencial. De este modo el programador sólo tiene que lidiar con las interacciones que pueden darse entre estados finales de transacciones, en lugar de tener que razonar sobre las interacciones a bajo nivel de su código con el resto del sistema. Adicionalmente el uso de transacciones permite componer varias transacciones individuales simplemente encapsulándolas en una transacción mayor. El motor de la base de datos es el encargado de mantener la consistencia del sistema y permite abstraer al programador de buena parte de la complejidad de la programación paralela a través de una interfaz sencilla y comprensible.

En 1977 Lomet propone utilizar una abstracción similar como mecanismo para garantizar la consistencia de datos compartidos entre diferentes procesos [71]. Introduce el concepto de atomic actions como una interfaz para especificar que una serie de instrucciones deben ser atómicas, dejando la responsabilidad del control de la concurrencia al sistema que implemente esta interfaz en lugar de al programador. En 1993 Herlihy introduce el término memoria transaccional (TM) con un propósito similar, y propone una arquitectura multiprocesador que hereda el concepto de transacción del modelo de programación utilizado en bases de datos [56]. Además incluye una implementación hardware para dar soporte a esta arquitectura.

La popularización de los CMP ha renovado el interés en la investigación sobre TM. Desde principios de los 2000 han aparecido numerosas propuestas de sistemas TM, tanto hardware como software. Estas últimas han sido especialmente atractivas desde el punto de vista de la investigación, ya que han permitido desarrollar algoritmos más complejos que se alejan de las limitaciones inherentes

al hardware. Sin embargo añaden una instrumentación al código para mantener la consistencia del sistema que va en detrimento del rendimiento, especialmente en códigos en los que éste viene limitado de por sí por los accesos a memoria (memory-bounded).

En los últimos años, varios fabricantes de procesadores como Intel, IBM o AMD han desarrollado propuestas destinadas a soportar TM en sus arquitecturas. Intel añadió un conjunto de instrucciones a su ISA para ofrecer soporte HTM básico en su línea de procesadores de consumo a partir de la familia Haswell [112]. IBM ha añadido también este soporte en su línea de procesadores POWER [66] a partir de POWER8 y en sus series de *mainframes* Blue Gene [110] y System Z [59]. AMD por su parte propone extensiones similares, aunque aún no las ha incluido en sus arquitecturas [17]. En todos estos casos el procesador se encarga de la detección y gestión de conflictos entre transacciones pero no garantiza su eventual finalización, dejando en manos del desarrollador la implementación de una ruta software alternativa para estas transacciones. Estos diseños se conocen como *best-effort*, haciendo referencia a que el procesador intentará ejecutar la transacción sin proporcionar garantías de que pueda finalizar. Aun con ésta y otras limitaciones, representan un hito al ser las primeras implementaciones reales de TM en procesadores de consumo.

#### 1.2.1. Ventajas de la memoria transaccional

En el contexto de TM, definimos una *transacción* como un conjunto de instrucciones máquina ejecutadas por un mismo proceso de forma atómica y serializable. Con atómica nos referimos a que los cambios que realice la transacción durante su ejecución son invisibles al resto de procesos concurrentes hasta que ésta finalice (*commit*), momento en el cual todos los cambios se propagarán al resto de hilos sin que éstos puedan observar un estado intermedio de dichos cambios. En caso de que el sistema TM detecte algún conflicto durante la ejecución de la transacción, ésta abortará sin propagar ningún cambio al resto del sistema. Con serializable nos referimos a que la historia de cambios que realice un conjunto de transacciones debe corresponder a la que se obtendría ejecutando secuencialmente *en algún orden* dichas transacciones. Un sistema TM, por tanto, ejecutará transacciones de forma concurrente garantizando estas propiedades. Para ello detectará y resolverá posibles conflictos entre transacciones que puedan violar dichas propiedades, generalmente abortando alguna de las transacciones implicadas.

La atomicidad y la serializabilidad, al igual que la ausencia de restricciones de orden, son características comunes entre las transacciones utilizadas en bases

de datos y las utilizadas en TM. Sin embargo, su propósito es diferente. De este modo, en un sistema TM, las transacciones están pensadas para tener una vida corta, acceder a un número limitado de posiciones de memoria y residir en una memoria volátil del sistema, generalmente a nivel de caché. Idealmente la duración de una transacción no debería exceder de un *scheduling quantum* del sistema operativo [56]. Por su parte, las transacciones utilizadas en bases de datos no tienen una duración limitada, pueden acceder a un número arbitrario de posiciones de memoria y son no volátiles, lo que implica que sus cambios se almacenan en memoria no volátil del sistema. De aquí en adelante cuando hablemos de transacciones nos referiremos siempre a un contexto de TM.

Además de simplificar la programación paralela, TM permite aplicar los conceptos de abstracción y composición. Por una parte no es necesario conocer los detalles de implementación de una función para utilizarla. Por otra parte es posible construir métodos complejos que mantengan la atomicidad combinando varias transacciones en una transacción mayor. Esta idea se conoce como *anidamiento de transacciones* [55], y puede soportarse de diferentes maneras. En esta tesis se hará uso de este concepto en el capítulo 4.

Para ilustrar lo anterior, consideremos de nuevo el ejemplo de la clase account visto en la sección 1.1. Con soporte TM, los métodos para retirar o ingresar dinero estarían ahora contenidos en sendas transacciones. Si dos hilos intentan actualizar a la vez una cuenta, el sistema TM detectaría un conflicto, que resolvería abortando una de las transacciones y reejecutándola posteriormente, evitando así problemas como *deadlocks* o *convoying*. Además sería posible utilizar la composición de los dos métodos para implementar una función de transferencia: bastaría con encapsular el código necesario en una transacción, sin necesidad de conocer la implementación de los métodos de ingresar o retirar efectivo.

#### 1.2.2. Técnicas de especulación con soporte transaccional

Por su modelo de concurrencia optimista, algunos autores han propuesto utilizar TM como plataforma para soportar modelos de especulación a nivel de hilo (*Thread-Level Speculation*, TLS) [87, 80, 109]. La idea aquí es aprovechar el sistema TM para aumentar el rendimiento de aplicaciones secuenciales ejecutando especulativamente y en paralelo código cuyas dependencias son difíciles de analizar estáticamente. Un ejemplo son bucles cuyas iteraciones realizan accesos a posiciones de memoria irregulares. Aprovechar aquí TM generalmente pasa por ejecutar el bucle en paralelo encapsulando sus iteraciones en distintas transacciones y manteniendo al menos un hilo *safe*, que no ejecutará código especulativo. En un

contexto TLS es necesario añadir restricciones de orden a las transacciones de modo que cada transacción haga visibles sus cambios en el orden natural de las iteraciones del bucle. De este modo, si el bucle no tenía dependencias, o éstas eran escasas, es posible extraer paralelismo en códigos secuenciales. Aunque este modelo de paralelismo mediante especulación no requiere el uso de TM, ésta proporciona características deseables como la detección de conflictos o la gestión de versiones que facilitan su implementación.

#### 1.2.3. Operaciones de reducción y memoria transaccional

Las reducciones son un conjunto de operaciones de la forma  $O=O\oplus\xi$ , que implican una lectura y posterior escritura sobre una misma variable (O) a través de un operador asociativo y conmutativo denominado *operador de reducción*  $(\oplus)$ . Estas operaciones aparecen con frecuencia en aplicaciones científicas, por lo que su optimización ha sido objeto de estudio, existiendo diversas técnicas para su paralelización eficiente [50,31,86,41]. Una limitación de estas técnicas, sin embargo, es la necesidad de garantías de que la variable objeto de la reducción O no sea accedida fuera de la operación de reducción y de que el valor a reducir  $\xi$  no dependa de O. Esto requiere un alto grado de conocimiento acerca del algoritmo a implementar, o bien un análisis de dependencias que garantice que los accesos de reducción mantengan estas propiedades durante la ejecución del programa. Dicho análisis no siempre es posible, especialmente en problemas con patrones de acceso irregulares, cuyas dependencias a menudo no son conocidas hasta el momento de la ejecución.

El uso de TM en este tipo de códigos irregulares puede facilitar su paralelización, pero no es una solución óptima debido a los conflictos que puede implicar la presencia de reducciones. Al consistir éstas en una lectura seguida de una escritura en una estructura compartida, el sistema TM puede detectar accesos de reducción realizados por transacciones diferentes como conflictos de datos, perjudicando el rendimiento. Existen propuestas de sistemas TM que evitan detectar estos accesos como conflictos, pero requieren de las mismas garantías que el resto de técnicas mencionadas [43].

### 1.3. Motivación y contribuciones

El uso de TM como herramienta para la implementación de secciones críticas puede facilitar la programación de códigos paralelos. Sin embargo, el rendimiento

obtenible utilizando TM está condicionado en gran medida por la tasa de abortos producidos durante la ejecución. Dichos abortos dependen de los conflictos generados por las transacciones y de la política de detección y resolución de los mismos que implemente el sistema TM.

En el caso de las operaciones de reducción se da la paradoja de que semánticamente pueden intercalarse reducciones ejecutadas por hilos diferentes sin alterar el resultado final siempre que cada operación individual sea atómica y que las condiciones de la reducción se mantengan a lo largo de la ejecución del programa. Sin embargo, dado que el sistema TM no es capaz de distinguir este tipo de accesos, producirá abortos por conflictos de datos que pueden ser innecesarios. Dichos abortos serían evitables si se tratasen adecuadamente por parte del sistema TM. Esto sería además especialmente útil en problemas con patrones de acceso irregulares, que dificultan en gran medida un análisis estático del conjunto de datos de reducción así como de la validez de las condiciones de reducción a lo largo de la ejecución del programa. Ante esta situación, la primera pregunta que motiva esta tesis es:

¿Tiene sentido tratar las reducciones como una operación independiente en un modelo de memoria transaccional?

Por otra parte, un denominador común en el uso de soporte TM para implementar modelos de especulación son las restricciones totales de orden entre transacciones. Hay varias propuestas que utilizan un sistema TM para detectar posibles dependencias entre hilos especulativos y no especulativos. Dichas propuestas se suelen basar en el establecimiento de una ordenación secuencial entre transacciones que permita mantener uno de los hilos ejecutando código no especulativo. Sin embargo, tras comprobar experimentalmente que la penalización en rendimiento que implica mantener una restricción estricta de orden entre transacciones a menudo impide extraer rendimiento en aplicaciones, proponemos relajar dichas restricciones a un modelo de orden parcial, que afecte a conjuntos de transacciones y permita finalizar simultáneamente transacciones de un mismo conjunto sin necesidad de serializar la fase de commit de las mismas. Por tanto, la segunda pregunta motivadora de esta tesis es:

¿Tiene sentido introducir restricciones de orden totales o parciales en un modelo de memoria transaccional?

Los capítulos 3 y 4 de este trabajo tratan de dar respuesta a ambas preguntas. El primero explora el soporte de operaciones de reducción en los sistemas TM y sus

implicaciones en el diseño y la implementación de estos sistemas. El segundo se centra en el soporte de restricciones parciales de orden entre transacciones para mejorar los modelos de especulación basados en un orden estricto de precedencia entre transacciones.

Las principales contribuciones de esta tesis son las siguientes:

- Ampliación del modelo TM para soportar operaciones de reducción transaccionales. Este modelo permite la concurrencia de las operaciones de reducción de distintas transacciones sin producir abortos siempre que sea posible, a la vez que detecta posibles violaciones de las propiedades de reducción en tiempo de ejecución.

- Inclusión de restricciones de orden total para dar soporte a códigos con reducciones parciales, donde las condiciones de reducción sólo se cumplen en un subconjunto del total de direcciones que presentan accesos de reducción. Esto permite que el programador pueda indicar patrones potenciales de reducción en el código sin necesidad de garantizar las propiedades de dichas reducciones a lo largo de la ejecución del programa.

- Adaptación del modelo anterior a sistemas TM reales. Concretamente se proponen dos implementaciones software que usan como base algoritmos de sistemas STM del estado del arte.

- Introducción de un modelo de orden parcial en TM, que ordene entre sí conjuntos de transacciones en lugar de transacciones individuales. De este modo, las transacciones pertenecientes a un mismo conjunto pueden finalizar sin restricciones, pero se garantiza que todas las transacciones de un conjunto anterior han terminado antes de que cualquiera de las transacciones de un conjunto posterior puedan hacer visibles sus cambios.

- Introdución del concepto de barrera transaccional como primitiva para soportar el modelo de orden parcial. Se trata de una directiva dentro de un entorno TM con la misma semántica que una barrera de sincronización tradicional, pero que permite que los hilos continúen la ejecución de forma especulativa sin bloquearse. Esta directiva proporciona al sistema TM información sobre el estado de ejecución de los diferentes hilos que permiten establecer un orden de precedencia parcial en tiempo de ejecución.

- Implementación del modelo de orden parcial con barreras transaccionales en un sistema de TM hardware real.

Estas contribuciones están orientadas a dotar a los sistemas TM de soporte a restricciones de orden y a operaciones de reducción, y a estudiar las posibilidades que habilita dicho soporte de cara a la paralelización de aplicaciones.

#### Estructura de la tesis 1.4.

El resto de esta tesis está estructurado como sigue.

El capítulo 2 ofrece una perspectiva de la memoria transaccional desde diferentes ejes. En él se detallan los principales aspectos a tener en cuenta desde un punto de vista del diseño de sistemas TM, y se incluye un estudio de las diferentes visiones de la semántica transaccional que se pueden encontrar en la literatura. El capítulo concluye con un breve análisis de una selección de sistemas TM software, hardware e híbridos relevantes para esta tesis.

El capítulo 3 presenta nuestro trabajo para el soporte de reducciones y restricciones de orden total en TM. Incluye un estudio de diferentes aproximaciones para abordar la paralelización de códigos que incluyen reducciones, el diseño e implementación de los sistemas TM desarrollados y su evaluación en un conjunto de escenarios de interés. Este capítulo comprende las tres primeras contribuciones antes descritas.

El capítulo 4 presenta nuestro trabajo para el soporte de restricciones de orden parcial en sistemas HTM. Incluye un estudio de las limitaciones y características relevantes de los sistemas HTM de consumo a los que va orientada nuestra propuesta, el diseño e implementación de la misma en forma de barreras transaccionales, y su correspondiente evaluación en una serie de aplicaciones de interés. El capítulo comprende las tres últimas contribuciones de esta tesis.

El capítulo 5 concluye la tesis, sintetiza las contribuciones publicadas y ofrece posibles líneas de trabajo para extender las propuestas presentadas.

Adicionalmente, el apéndice A detalla la API<sup>2</sup> utilizada a lo largo de este trabajo, basada en trabajos anteriores sobre TM, y las ampliaciones realizadas para soportar las propuestas de los capítulos 3 y 4.

<sup>&</sup>lt;sup>2</sup>Acrónimo de *Application Programming Interface* (interfaz de programación de aplicaciones).

## Capítulo 2

## **Antecedentes**

Este capítulo ofrece una perspectiva de la memoria transaccional (TM) desde diferentes ejes. La sección 2.1 introduce las transacciones y sus propiedades básicas. La sección 2.2 describe una interfaz mínima de TM que se utilizará en el transcurso de la tesis. La sección 2.3 ofrece una visión de las diferentes decisiones de diseño a considerar a la hora de implementar sistemas TM. La sección 2.4 incluye consideraciones adicionales respecto a la semántica de las transacciones. En ella se detallan diferentes criterios a la hora de definir propiedades de las transacciones como la atomicidad, la consistencia o el anidamiento. Finalmente, la sección 2.5 analiza varias implementaciones de sistemas TM, incluyendo diseños software, hardware e híbridos. Esta sección incluye una revisión de las extensiones desarrolladas para el soporte de memoria transaccional en los procesadores más recientes.

## 2.1. Transacciones

Una transacción es una secuencia de acciones que se muestran como indivisibles e instantáneas a un observador externo [55]. Tradicionalmente se han establecido cuatro garantías que deben cumplir las transacciones, conocidas como propiedades ACID³ [63]:

Atomicidad: una transacción requiere que sus cambios sean visibles de forma completa e instantánea, o que no sean visibles en absoluto. Esto implica

<sup>&</sup>lt;sup>3</sup>Acrónimo de Atomicity, Consistency, Isolation, Durability.

que toda transacción tiene dos finales posibles: finalizar con éxito, haciendo visibles sus cambios de forma instantánea al resto del sistema; o deshacer sus cambios hasta el instante del inicio de la transacción sin que el sistema detecte evidencia alguna de su ejecución. En el primer caso hablamos del *commit* de la transacción, mientras que en el segundo caso decimos que la transacción ha *abortado* su ejecución. La sección 2.4.1 ofrece un análisis más detallado de esta propiedad.

- Consistencia: dado que las transacciones modifican el estado de un sistema, esta propiedad implica que sus cambios deben partir de un estado consistente del mismo, y deben dejar otro estado también consistente al finalizar. Qué implica un estado consistente depende de la aplicación particular que se esté ejecutando, y hace referencia a los valores posibles que pueden tomar sus estructuras de datos en cada momento. La sección 2.4.2 analiza diferentes criterios de consistencia para TM propuestos en la literatura.

- Aislamiento: esta propiedad hace referencia a la necesidad de que una transacción no pueda interferir con el resto de transacciones concurrentes durante su ejecución. Garantizar el aislamiento requiere que el sistema TM detecte y resuelva las posibles interacciones que puedan producirse entre transacciones. Esta garantía es una de las diferencias más notables entre las transacciones y otras primitivas para la programación paralela y uno de los motivos del atractivo de TM como modelo de programación. La sección 2.3 ahonda en los mecanismos que permiten estas garantías.

- Durabilidad: implica que los cambios que realice una transacción exitosa sean permanentes en el sistema —se almacenen en memoria no volátil, e.g. un disco duro—, y estén disponibles para cualquier transacción posterior.

Estas cuatro propiedades provienen del modelo de transacciones utilizado en bases de datos. El paradigma de TM, sin embargo, no considera la durabilidad, ya que trabaja con datos inherentemente volátiles —memoria principal y caché—; ni contempla un criterio único de consistencia, al ser ésta dependiente de la aplicación concreta. Podemos decir por tanto que las propiedades básicas a garantizar por un sistema TM son la *atomicidad* y el *aislamiento* de las transacciones. La combinación de ambas propiedades produce la *serializabilidad* de las transacciones [83], que es el criterio de consistencia base de un sistema transaccional<sup>4</sup>.

```

1  // API TM básica

2  TmBegin();

3  bool TmEnd();

4  void TmAbort();

5

6  // Funciones adicionales para TM explícitos

7  T TmRead(T* addr);

8  TmWrite(T* addr, T val);

```

Figura 2.1: Interfaz transaccional mínima.

## 2.2. La interfaz transaccional

A lo largo de esta tesis utilizaremos una interfaz mínima para referirnos a TM en cualquiera de sus formas similar a la mostrada en la figura 2.1. Distinguimos tres operaciones básicas, similares al modelo original de Herlihy [56] y las complementamos con dos operaciones adicionales que permiten anotar los accesos transaccionales de lectura y escritura en sistemas TM que lo necesiten. Las funciones TmBegin y TmEnd delimitan el bloque de instrucciones que constituyen el cuerpo de la transacción. Cualquier acceso a memoria entre estas dos instrucciones será vigilado por el sistema TM para detectar posibles conflictos. La instrucción TmEnd intentará consolidar en memoria los cambios tentativos que haya realizado la transacción hasta el momento y devolverá si ha tenido éxito o no. Por su parte, la función TmAbort descarta los cambios realizados por la transacción desde el inicio de la misma hasta la llamada a TmAbort. Una transacción fallida restaurará el estado de la ejecución al momento inmediatamente posterior a la llamada a TmBegin.

Como se describirá en la sección 2.5.1, en sistemas TM explícitos es necesario especificar qué datos queremos que sean transaccionales. En estos sistemas son necesarias dos funciones adicionales que permitan realizar un acceso transaccional de lectura o escritura sobre una posición de memoria. TmRead lee el dato de la posición de memoria addr que se pasa como parámetro y devuelve su valor. El dato pasará a formar parte del conjunto de datos transaccional de lectura. TmWrite escribe transaccionalmente el valor val en la posición de memoria addr que se pasa como parámetro. Dicho dato pasará a formar parte del conjunto de datos transaccional de escritura.

En el apéndice A se ofrecen detalles adicionales de la interfaz transaccional utilizada a lo largo de este trabajo, incluyendo las primitivas propuestas en las contribuciones de los capítulos 3 y 4, *callbacks* adicionales para compatibilizar la interfaz con diferentes implementaciones TM y ejemplos de uso.

Figura 2.2: Control de concurrencia pesimista (izquierda) y optimista (derecha). Las flechas azules indican cuándo se produce un conflicto, las flechas rojas indican cuando se detecta por el sistema TM, las cruces indican cuándo se resuelve.

## 2.3. El espacio de diseño en memoria transaccional

A la hora de soportar la interfaz que hemos descrito en la sección 2.2 es necesario considerar una serie de decisiones de diseño que cubren diferentes aspectos de un sistema TM. Estos aspectos no son ortogonales, por lo que algunos condicionarán otras decisiones o limitarán el espacio de diseño en mayor o menor medida. En esta sección se analizan las principales cuestiones a tratar en el diseño de un sistema TM.

#### 2.3.1. Control de concurrencia

En el plano más general, la función de un sistema TM es arbitrar el acceso concurrente de distintos hilos de ejecución a datos compartidos, lo que se traduce en detectar y resolver adecuadamente posibles conflictos en el acceso a estos datos. En general distinguiremos los accesos de lectura y de escritura a un objeto compartido y consideraremos que se ha producido un conflicto cuando dos transacciones diferentes accedan concurrentemente a un objeto compartido y al menos uno de estos accesos sea de escritura. El sistema transaccional resolverá el conflicto abortando o retrasando alguna de las transacciones implicadas.

Podemos distinguir tres eventos ante un conflicto: cuándo se *produce*, cuándo se *detecta* y cuándo se *resuelve*. Dependiendo del diseño del sistema TM estos eventos pueden producirse de forma simultánea o en instantes diferentes, siempre que lo hagan en el orden anterior. En el primer caso hablamos de control de concurrencia *pesimista*: cuando se produce un acceso a un objeto compartido, el sistema TM detecta posibles conflictos y los resuelve, abortando o retrasando alguna de las