ELSEVIER

Contents lists available at ScienceDirect

# **Computers & Security**

journal homepage: www.elsevier.com/locate/cose

# A survey on the (in)security of trusted execution environments

Network, Information and Computer Security (NICS) Lab, University of Malaga, Spain

#### ARTICLE INFO

Article history: Received 16 November 2022 Revised 4 February 2023 Accepted 9 March 2023 Available online 14 March 2023

Keywords:

Computer security

Secure hardware

Trusted execution environments

Hardware attacks

Software attacks

Side-channel attacks

#### ABSTRACT

As the number of security and privacy attacks continue to grow around the world, there is an ever increasing need to protect our personal devices. As a matter of fact, more and more manufactures are relying on Trusted Execution Environments (TEEs) to shield their devices. In particular, ARM TrustZone (TZ) is being widely used in numerous embedded devices, especially smartphones, and this technology is the basis for secure solutions both in industry and academia. However, as shown in this paper, TEE is not bullet-proof and it has been successfully attacked numerous times and in very different ways. To raise awareness among potential stakeholders interested in this technology, this paper provides an extensive analysis and categorization of existing vulnerabilities in TEEs and highlights the design flaws that led to them. The presented vulnerabilities, which are not only extracted from existing literature but also from publicly available exploits and databases, are accompanied by some effective countermeasures to reduce the likelihood of new attacks. The paper ends with some appealing challenges and open issues.

© 2023 The Author(s). Published by Elsevier Ltd. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/)

#### 1. Introduction

Nowadays, a wide range of mechanisms are emerging to mitigate current and future security threats associated with the development of an ever increasing number of heterogeneous computing devices. Computing platforms are continuously evolving, running sophisticated operating systems and hosting countless applications from possibly untrustworthy vendors. In these highly complex environments, the risk of a security breach is extremely high and hence the need for execution environments capable of isolating security-sensitive applications. The inclusion of secure execution environments enables them hosting a wide variety of applications and protecting the integrity of their own internal state.

Among these mechanisms, a relevant choice is the use of Trusted Execution Environments (TEE), which are hardware-isolated areas in microprocessors that enable the secure execution of applications thereby assuring the confidentiality and integrity of data and code. In fact, in the definition of the TEE standard (Ekberg et al., 2012) it appears as an isolated environment that coexists and cooperates with the operating system. The main purpose of this isolation is to provide security to the whole system. TEE technology is certainly a trend in modern platforms, due

E-mail addresses: amunoz@lcc.uma.es (A. Muñoz), ruben@lcc.uma.es (R. Ríos), roman@lcc.uma.es (R. Román), jlm@lcc.uma.es (J. López).

in part to the adoption of smartphones as our primary platform of interaction with other devices.

ARM's TrustZone design stands out among the various system-on-chip (SoC) isolation solutions. TrustZone (TZ) is the collection of hardware mechanisms that enable TEEs to implement the required isolation from the main operating environment. TEEs have been considered as secure elements and as such have been used for protecting sensitive applications in a number of verticals, such as cyber-physical systems (CPS) (Pinto et al., 2017) or embedded systems (Janjua et al., 2019). Nevertheless, some recently found vulnerabilities and attacks on different TEE implementations, should make us re-examine existing assumptions on the security provisions of TEEs.

There are various works, such as (Komaromy, 2018; Lipp et al., 2016; Machiry et al., 2017; Rosenberg, 2014; Tang et al., 2017), that provide a nice perspective on the situation of security in TEE. In addition, other works provide additional analyses on this subject. For example, Sabt et al. (2015) describe the fundamental properties of TEE and provide a comparative study of different TEEs based on ARM TZ, but this work does not analyze their impact nor discuss the main reasons that may lead to attacks. Other examples, such as Arfaoui et al. (2014), provide a perspective according to GlobalPlatform (GlobalPlatform) standards, in terms of security, with various TEE technologies, and Asokan et al. (2014) present a comprehensive review of the current role of trusted computing technology in the field of mobile devices.

<sup>\*</sup> Corresponding author.

Our approach differs from the aforementioned papers in the sense that our study focuses on classifying existing vulnerabilities and identifying their impact on the different TZ-based TEE implementations. For this purpose, various devices in the market have been taken as a reference. Note that there have been other papers that analyze such issues, but only partially. For example, Santos et al. (2014) provide a taxonomy of vulnerabilities in commercial TEE, but without delving into the particularities of the attacks. Another example is Cerdeira et al. (2020), which provide an analysis of the security vulnerabilities found, until then, in those commercial TEE implementations based on TrustZone. Their paper was limited to the analysis of Qualcomm<sup>1</sup>, Trustonic, Huawei, Nvidia (Corporation, 2015) and Linaro OP-TEE Brand TEE systems. Finally, other works, such as Busch et al. (2020) and Meng et al. (2018) also provide a thorough critical review, although limited to Huawei's TEE and Android vulnerabilities, respectively.

This paper includes an exhaustive analysis of the security limitations and associated countermeasures of TrustZone-based TEEs. More specifically, the main contributions of this paper are as follows:

- An extensive review and analysis of the state of the art of TZ security extensions, including TEE implementations and their features.

- 2. A comprehensive categorization of existing vulnerabilities and attacks against TEE implementations.

- 3. A detailed analysis of existing countermeasures for the described attacks and vulnerabilities.

- 4. A discussion on open challenges and recommendations for future implementations of secure TEEs.

The rest of the paper is organized as follows: Section 2 provides a relevant background on TEE including the evolution of the standardization, a description of its main capabilities and applications, and some implementation details. Section 3 presents a novel taxonomy of TEE attacks that will guide the exposition throughout the rest of the paper. Software-based attacks are detailed in Section 4, architectural attacks in Section 5. Side-channel attacks are analyzed separately in Section 6 and micro-architectural attacks in 7. In Section 8 a series of existing countermeasures are compiled and analyzed. Finally, open challenges are discussed in Section 9, and conclusions and future works are presented in Section 10.

# 2. Background

# 2.1. The evolution of trusted execution environments

Software security mechanisms are not sufficient to counter advanced attacks in many real-world situations. In such cases, building secure solutions requires the involvement of secure hardware elements. Doubtlessly, the need for secure elements boosted the development of the TPM (Trusted Platform Module), whose first version dates from 2003 and was followed by TPM 2.0 (TCG, 2013), which appeared several years later, in 2012. However, both of these standards have been considered unsuitable for mobile computing devices for various reasons, such as limitations derived from the use of batteries, the computational restrictions imposed by mobile devices or the increased price implied by the integration of a TPM chip, which in some cases can represent a high percentage of the device's hardware budget. In this line, the Trusted Computing Group (TCG) (TCG, 2013) defined in 2007 the specifications of the Mobile Trusted Module (MTM) (Ekberg et al., 2007), which appears as an branch of TPM v1.2 with changes to adapt it to mobile

platforms. Nevertheless, as a consequence of the physical resource limitation of mobile devices, but MTM implementation was never widely adopted. Later TPM Mobile (McGill, 2013) was proposed as an attempt to adapt the TPM 2.0 specification to mobile devices. Although that specification was designed to cover implementation on a wide range of mobile devices, TPM Mobile was only implemented in a small number of devices due to the lack of trust in a software-based solution. There have been alternative implementations of a mobile TPM, such as simTPM (Chakraborty et al., 2019), which relies on the SIM card available in mobile platforms to avoid most of mobile TPM and MTM issues without the need for additional hardware. Notwithstanding, the main disadvantage with this solution was that the SIMs were not tamper-proof resistant, unlike the TPM chip, and therefore cannot be considered as a reliable secure element.

As a consequence of these issues, GlobalPlatform<sup>2</sup>, a non-profit association, defined specifications for secure chip technologies, gathering the fundamental security requirements of mobile devices and describing the ideal security guard for mobile devices. This specification, known as Trusted Execution Environment (TEE), quickly gained traction on the market - to the point that a number of companies that were initially reluctant to the initiative finally joined. TEE architecture proposed by GlobalPlatform highlighting the separation of worlds<sup>3</sup> as the most relevant design novelty. Nokia and Trusted Logic were the first in the long list of companies that joined, followed by other companies such as ARM, NVIDIA (Corporation, 2015), AMD, ST, Qualcom, Ericsson and Samsung, which are now fully involved in the development of the TEE specifications. As of today, TEE is a well-defined security element, whose technical specifications not only define the architecture but also the services available for the applications running on top of it<sup>4</sup>. GlobalPlatform initially focused on TEE standardization (System Architecture specifications and client API interface). Later, GlobalPlatform released a specification for the Secure OS, including the internal API and TEE applications.

The main goal of the TEE is to guarantee the *secure execution* of programs<sup>5</sup> For this purpose, TEE isolation capability enables a secure area for handling sensitive data, thus eliminating the need to trust the software running in the device. In particular, ARM Trust-Zone (Pinto and Santos, 2019), which is the most extended trusted hardware TEE systems rely on, defines two protection domains or realms: the Secure World (SW) and the Normal World (NW).

# 2.2. TEE capabilities and applications

The TEE design enables to implement security-sensitive services by taking advantage of its assurance and secure storage functionalities necessary to preserve both the confidentiality and integrity of data and code. In current implementations, the decision to deny or allow the installation of a new service in the TEE is made by the TEE developer playing the role of a central authority.

Among the different capabilities offered by the TEE, we highlight the following:

Isolated execution: This functionality allows the separated execution of applications, some of them in a secure environment and others in a normal environment. It is highly recommended that isolation is achieved by means of hardware mechanisms in order to prevent this mechanism from being controlled from

<sup>&</sup>lt;sup>1</sup> Qualcomm Product Security. Available: https://www.qualcomm.com/company/productsecurity/securityadvisories.

<sup>&</sup>lt;sup>2</sup> https://globalplatform.org/.

$<sup>^{3}</sup>$  Some authors refers to realms instead of worlds, both terms are the same concept along this paper.

<sup>4</sup> http://globalplatform.org/specificationsdevice.asp.

<sup>&</sup>lt;sup>5</sup> Henceforth, we use indistinguishably the terms trustlets and trusted applications (TAs) to software executed in the TEE as secure programs, applications or processes.

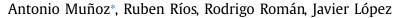

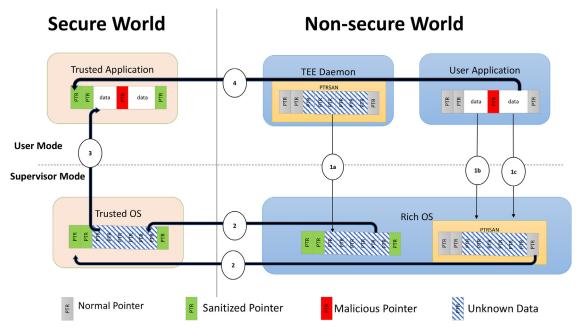

Fig. 1. Relationship between the Secure World and the Normal World.

the non-secure world. Isolated execution can be considered as the primary purpose of a TEE.

- Secure Storage: The TEE provides Trusted Storage of data and keys. Trusted storage is tied to a particular TEE and device. This prevents any attacker from accessing and modifying the stored data unless they have the appropriate permissions.

- Platform Integrity: Secure boot ensures both the integrity and authenticity of the platform. It allows the trusted OS execution environment to be instantiated from a trusted root within the TEE. The process uses assets linked to the TEE and isolated from the normal OS. Besides, according to the TEE description, the TEE is protected against some physical attacks. However, note that attacks breaking the IC package are beyond the scope of TEE protection.

Based on the above core capabilities, existing TEEs, such as TrustZone, can build a large variety of functionalities and applications. Some examples are secure credentials generation (Elenkov, 2013), secure key storage (Android Keystore, dmverity) (Cooijmans et al., 2014), secure boot (Dietrich and Winter, 2009; Ge et al., 2014), kernel integrity verification, (e.g., Samsung's TIMA Azab et al. (2014)), trusted peripherals and sensors (Liu et al., 2012), mobile payments using emulation of secure elements (Pirker and Slamanig, 2012; Pirker et al., 2012), digital content protection systems (Ahmad et al., 2013; Tögl et al., 2013), services to manage and issue online tickets (Hussin et al., 2005; 2006; Tamrakar et al., 2011), cloud storage access authentication mechanisms (Ekberg et al., 2012; Shin et al., 2012), security of IoT devices (González and Bonnet, 2013; Guan et al., 2017), and many more.

# 2.3. Trusted execution environment & ARM TrustZone architecture

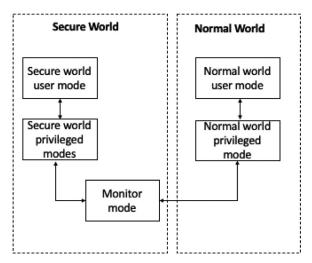

As mentioned above, ARM TrustZone is a particular implementation of TEE that enables the isolation of CPU state, memory, I/O data, etc. It is built around the concept of protection domains, namely the SW and NW, as aforementioned. This system-wide approach assign two virtual cores (in the SW and NW respectively) to each physical processor, together with the mechanism to securely switch between both realms (cf. Qualcomm TEE in Fig. 2). In most cases, a security-oriented OS is deployed on the TEE, which operates and hosts a number of trusted applications (TAs).

The separation between worlds is articulated by different interrupts, I/O hardware, memory views, etc. while prioritizing requests from the SW. This process is orchestrated by means of the *monitor mode mechanism*, which plays the role of the gatekeeper by switching between realms (Sabt et al., 2015).

**Fig. 2.** TEE Worlds in Qualcomm TEE. Communication between wolds is mediated by a priviledged OS daemon by SMC calls.

The secure monitor call (SMC) is the component in charge of actually implementing the monitor mode mechanism. SMC requests switching between worlds (secure and normal). Besides, the SMC provides an API within system calls (syscalls) for inter-realms communications. For example, whenever a process running in the NW needs any service provided by a TA, a run state transfer is requested from the NW to the SW kernel (Holding, 2009).

Memory sharing between realms is articulated with two functions *SMC\_TYPE\_FAST* and *SMC\_TYPE\_YIELD*<sup>6</sup>. *SMC\_TYPE\_YIELD* is used for the allocation of a memory area belonging to the NW to be shared with SW, which is particularly useful when high-volume data transfers are involved and in the case of synchronous trusted applications are needed (e.g., video streaming protection). On the other hand, *SMC\_TYPE\_FAST* enables a mechanism for fast information exchange. It relies on the use of registers with up to a total of four variables to perform data transfers between the two realms.

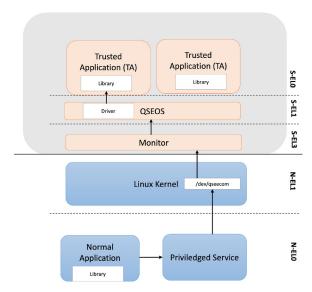

In Fig. 2, the Exception Level (EL) realms separation is depicted. In this line, N-EL1 means Exception level 1 in non-secure world while S-EL0 is Exception level 0 in secure world. The grey shaded area corresponds to the components that implement the secure world execution. Whereas the blue boxes are components that belong to the non-secure world.

Other components, such as the *TZASC* and *TZMA*, are used for memory management SRAM and DRAM respectively – as depicted in Fig. 3. These implement protection schemes for the static onchip and for the dynamic off-chip memory. As such, they prevent attempts to access memory within a memory controller by the TZ kernel from the normal global environment. In such a case, the CPU aborts and reacts according to the configured specification, i.e. rebooting the device due to a violation (Holding, 2009).

We notice how TrustZone architecture does not define the way to implement TAs accesses with TrustZone services. Indeed, there are TZ-based implementations with different service definitions, but all sharing the common architecture described.

Access properties are another aspect related to memory management articulated through memory page permissions. For example, those memory regions with write capability are filled up at runtime, and therefore must be located in a modifiable memory area. On the other hand, as in the case with code pages, which

<sup>&</sup>lt;sup>6</sup> ARM Trusted Firmware. (n.d.). (ARM & Linaro) Retrieved from https://www.trustedfirmware.org/.

Fig. 3. Architecture on TZ-assisted SoC.

only have read and execute permissions, they may not be modified in any way. The *Domain Access Control Register (DACR)* mechanism is in charge of restricting the access of TEE applications to memory regions of other trusted applications. This is implemented in the *Memory Management Unit*, or MMU. Certain bits (linked to a given memory region) are checked by MMU in the DACR register to specific access properties. In addition, the MMU is in charge of enabling read and write access to the memory allocated to that domain

Bus management connectivity is articulated using the *APB* and the *AXI* components. AXI is the bus interface implementation for the main system at the chip level. APB implements a low-bandwidth single peripheral bus interface. This interconnection between AXI and APB is implemented with a bridge. Among the different capabilities offered by the AXI interface is the separation of peripherals into realms, allowing both reliable and unreliable ones. For this purpose, it makes use of an extended signaling system together with a flag bit (NS-bit). There is no similar mechanism for the APB bus so the security is managed by the aforementioned AXI-to-APB bridge (Holding, 2009).

We have so far focused on describing the most relevant components to facilitate the understanding of the attacks and flaws presented in the following sections. A full description of the ARM architecture is beyond the scope of this paper, but interested readers can refer to (Ngabonziza et al., 2016) for further details on it.

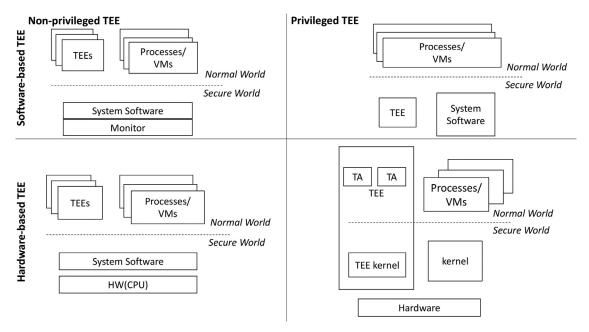

#### 2.4. TEE implementations

At present there are many different implementations of TEEs, and in the literature it is possible to find different criteria to classify them. The taxonomy presented in Fig. 4 focuses on how the TEE is implemented. On the one hand, there are implementations in which the TEE is implemented with software, such as Overshadow, OpenTEE, OPTEE, etc. On the other hand, there are various hardware implementations of TEE, including Intel SGX, Qualcomm, and others. Another parameter that is used to classify the different implementations is the level of privilege with which they are executed, i.e. if we are dealing with a privileged or non-privileged

TEE. Non-privileged TEEs support multiple deployments, allowing to include a new functionality by simply adding new instances without extending the system trusted computing base – which would increase the attack surface of the system. Most of these TEEs make use of a secure monitor from the design stage (which is usually software-based) or by taking direct advantage of hardware-supported secure enclaves (SGX, TPM, AMD-SEV, etc.). On the other hand, priviledged TEEs, in most cases, have access to all system resources.

Table 2 provides a classification of existing TEE implementations according to the taxonomy introduced in the previous paragraph – that is, hardware vs software implementations and privileged vs non-privileged implementations. Note, however, that there are two distinct groups of implementations among the privileged TEE hardware-based implementations. Firstly, there are commercial solutions (Trusty (Google), QSEE (Beniamini), Trustonic (Felton), etc.) and secondly, academic or open source solutions (OPTEE (Brand), Kinibi (Lapid and Wool, 2018), SafeG (Takei et al., 2009), etc.). In addition, we propose TPM as an alternative for Trusted Execution Environments.

# 2.5. Implementation details of qualcomm's secure execution environment

It is common practice for NW applications to require interaction with others running in SW. KeyStore is the process in charge of managing cryptographic keys in Android, which requires direct communication with the *KeyMaster*. This is a trusted application that provides key secure management using TrustZone capabilities (e.g., secure storage, isolation, etc.). Yet we have to consider that, on the basis of QSEE, user-mode applications are not allowed to perform SMC calls to enter the SW. This limitation is due to the fact that kernel-space privileges are required. In order to overcome this limitation, the Linux kernel driver QSEECOM – QSEE Communicator – allows user-space processes to access several TZ-based operations, such as those related to the communication with the loaded TAs or the actual loading of the TAs in the SW.

Fig. 4. TEE Implementation Classification.

**Table 1** Definitions.

| Acronym  | Definition                                | Acronym | Definition                                 |  |

|----------|-------------------------------------------|---------|--------------------------------------------|--|

| AES      | Advanced Encryption Standard              | PXN     | Privileged execute never                   |  |

| ALSR     | Address Space Layout Randomization        | QSEE    | Qualcomm Secure Execution Environment      |  |

| AMBA     | Advanced Microcontroller Bus Architecture | QSEECOM | QSEE Communicator                          |  |

| APB      | Advanced Peripheral Bus                   | REE     | Rich Execution Environment                 |  |

| AXI      | Advanced Extensible Interface             | ROM     | Read Only Memory                           |  |

| BTB      | Branch Target Buffer                      | RO-IoT  | Reboot Oriented IoT                        |  |

| CCNT     | Cycle Counter Register                    | ROP     | Return Oriented Programming                |  |

| CLI      | Command Line Interface                    | SC      | Stack Cookies                              |  |

| CPS      | Cyberphysical Systems                     | SCA     | Side Channel Attack                        |  |

| CRT      | Chinese Remainder Theorem                 | SCM     | Secure Channel Manager                     |  |

| DACR     | Domain Access Control Register            | SCP     | Secure Channel Protocol                    |  |

| DCISW    | Data Cache line Invalidate by Set/Way     | SCTRL   | System Control Register                    |  |

| DDR      | Double Data Rate                          | SGX     | Software Guard Extensions                  |  |

| DFA      | Deterministic Finite Automata             | SHA     | Secure Hashing Algorithm                   |  |

| DoS      | Denial of Service                         | SMC     | Secure Monitor Call                        |  |

| DVFS     | Dynamic Voltage and Frequency Scaling     | SMMU    | System Memory Management Unit              |  |

| EMFI     | Electromagnetic Fault Injection           | SoC     | System on a Chip                           |  |

| FDE      | Full Disk Encryption                      | SVC     | Service Message                            |  |

| FIFO     | First In First Out                        | SVE     | System Vulnerability & Effectiveness       |  |

| FIQ      | Fast Interrupt Query                      | SW      | Secure World                               |  |

| FPGA     | Field-Programmable Gate Array             | Syscall | System Call                                |  |

| GP       | Guard Page                                | TA      | Trusted Application or Trustlet            |  |

| IoT      | Internet of Things                        | TCB     | Trusted Computing Base                     |  |

| I/O data | Input/Output data                         | TCG     | Trusted Computing Group                    |  |

| IP       | Intellectual Property                     | TCI     | Trustlet Connector Interface               |  |

| IRQ      | Interrupt request                         | TEE     | Trusted Execution Environment              |  |

| L1       | Level One                                 | TEEv    | TEE Virtualized                            |  |

| L2       | Level Two                                 | TLC     | Trustlet Connector                         |  |

| MTM      | Mobile Trusted Module                     | TLV     | Type Length Value                          |  |

| NW       | Normal World                              | TPM     | Trusted Platform Module                    |  |

| MMU      | Memory Management Unit                    | TZ      | TrustZone                                  |  |

| MPU      | Memory Protection Unit                    | TZASC   | TZ Address Space Controller                |  |

| ОЬС      | On Board Credential                       | TZMA    | TZ Memory Adapter                          |  |

| OEM      | Original Equipment Manufacturer           | UART    | Universal Asynchronous Receiver/Transmitte |  |

| OTA      | Over The Air                              | UUID    | Universal Unique Identifier                |  |

| OP-TEE   | Open Portable TEE                         | UXN     | Unprivileged Execute never                 |  |

| OS       | Operating System                          | VBAR    | Vector Base Address Register               |  |

| OU       | Organizational Unit                       | XP      | Execution Protection                       |  |

| PLL      | Phase-Locked Loop                         | XPU     | External Protection Unit                   |  |

**Table 2** TEE Implementations.

|          | Non Privileged TEE                     | Privileged TEE                            |                                    |  |  |  |

|----------|----------------------------------------|-------------------------------------------|------------------------------------|--|--|--|

|          |                                        | Commercial                                | Open/Academic                      |  |  |  |

| Hardware | SecureBlue+(Boivie and Williams, 2012) | Google TrustyGoogle                       | Linaro OPTEEBrand                  |  |  |  |

| TEE      | Sanctum(Costan et al., 2016)           | Qualcomm QSEE(Qualcomm, 2018)             | ARMithril(Shah et al., 2012)       |  |  |  |

|          | AMD-SEV(AMD, 2021)                     | Trustonic t-baseFelton                    | GenodeTEE(Feske, 2015)             |  |  |  |

|          | OSP(Cho et al., 2016)                  | Samsung TZ-RKP(Azab et al., 2014)         | Microsoft TLR(Santos et al., 2014) |  |  |  |

|          | TrustICE(Sun et al., 2015b)            | AuroraLammens                             | Case(Zhang et al., 2016a)          |  |  |  |

|          | Sanctuary(Brasser et al., 2019)        | SierrawareSierraWare                      | TrustOPT(Sun et al., 2015a)        |  |  |  |

|          | Intel SGX(Intel, 2014)                 | Solacia SecuriTEESolacia                  | SafeG(Takei et al., 2009)          |  |  |  |

|          | Haven(Baumann et al., 2015)*           | mTower(Drozdovskyi and Moliavko, 2019)    | VimoExpress(Oh et al., 2012)       |  |  |  |

|          | SCONE*(Arnautov et al., 2016)          | T6TrustKernel                             | Kinibi_M(Trustonic, 2017)          |  |  |  |

|          | Graphene-SGX*(Tsai et al., 2017)       | ObC (Kostiainen et al., 2009)[deprecated] | Andix OS(Fitzek et al., 2015)      |  |  |  |

|          | Panoply*(Shinde et al., 2017)          |                                           |                                    |  |  |  |

| Software | Overshadow(Chen et al., 2008)          |                                           |                                    |  |  |  |

| TEE      | Virtual Ghost(Criswell et al., 2014)   | Nested Kernel(Dautenhahn et al., 2015)    |                                    |  |  |  |

|          | Inktag(Hofmann et al., 2013)           | OpenTEE(McGillion et al., 2015)           |                                    |  |  |  |

|          | Flicker(McCune et al., 2008)           | MicroTEE(Ji et al., 2019)                 |                                    |  |  |  |

|          | TrustVisor(McCune et al., 2010)        | SoftTEE(Lee and Park, 2020)               |                                    |  |  |  |

|          | Multizone(Pinto and Garlati, 2020)     | Trustshadow(Guan et al., 2017)            |                                    |  |  |  |

|          | Utango(Oliveira et al., 2021)          | Kinibi(Lapid and Wool, 2018)              |                                    |  |  |  |

|          | Sego(Kwon et al., 2016)                | SKEE(Azab et al., 2016)                   |                                    |  |  |  |

|          | SICE(Azab et al., 2011)                |                                           |                                    |  |  |  |

For the implementation of Secure Monitor calls from the kernel space an interface was included in the driver. This interface between QSEECOM and the SW is known as SCM, which is considered the widest attack surface of the TEE since is one of a small number of communication channels between the outside world and the SW. Therefore, a limited number of processes are allowed access to QSEECOM for the sake of security. As such, Beniamini's et al. Beniamini implementation limits the number of processes which can access the QSEECON from the normal world to only four:

- SurfaceFlinger (running with "system" user-ID): This is a system service in charge of the composition of the application and system surfaces, for which a shared buffer is enabled.

- DrmServer (running with "drm" user-ID): This element is in charge of managing digital rights.

- MediaServer (running with "media" user-ID): This element is in charge of handling multimedia services.

- KeyStore (running with "keystore" user-ID): This element is in charge of creating, storing and managing cryptographic keys.

Note that vulnerable processes should not have access to the TEE because if the vulnerability is exploited by an attacker, the attacker could gain access to any application running in the SW bypassing the Linux kernel filter on the process. A known weak point is the language in which trusted applications are written. Most applications use the C language instead of safe languages that potentially decrease the possibility of vulnerabilities.

The TrustZone fast and yield commands used for memory sharing are implemented by Qualcomm<sup>7</sup> using two functions: SMC\_TYPE\_YIELD and SMC\_TYPE\_FAST. The first one allocates a common memory area for communications between worlds. When this function is called a memory record is populated. The record includes the maximum buffer size, the buffer headers, as well as offsets of the data to be sent and received. The second is used to start a short-term communication where the data to be exchanged are relatively small. Either function can be used to issue an SMC or to call a service.

As previously mentioned, the first defense mechanism in this situations is the DACR provided by ARM, which prohibits altering

any of the TZ kernel pages. Some recent TrustZone-enabled Qualcomm System on a Chip (SoC) integrate an additional mechanism for memory access control. This hardware-based Memory Protection Unit (MPU) are pre-configured to mark as write-protected certain memory regions predefined by the manufacturer.

In Qualcomm these MPU units are called External Protection Units (XPUs). Among the tasks carried out by the XPUs is prevening access from the NW to the SW and to the memory areas restricted by the manufacturer. As an example, the XPU mechanism is used to allocate TrustZone kernel code into write-protected memory areas, which are checked during the secure boot of the system to ensure that it has not been altered.

One sensitive aspect is how to load trusted applications and their revocations when Qualcomm secure booting actually takes place. In this line, regular Executable and Linking Format (ELF) files are signed by Qualcomm. These files attach a single hash table segment, which is a signature blob with the hashes of each ELF segment, along with the certificate chain. Verification of the signature with the concatenated blob of hashes is performed with the public key of the attestation certificate (the last one in the chain). Validation is performed by comparing the hash of the root certificate and the *Root Key Hash* stored on the device. It is stored in the ROM of the device and integrated in the SoC.

We now briefly describe how the chain of trust workflow is implemented. The procedure begins with the issuance of a hardware-bound key for the validation of the certificates. Later, these certificates can be used to validate the binary signature. In addition, Qualcomm includes additional Organizational Unit (OU) fields with information necessary for security enhancement in the binary signatures.

Note that since TEEs are considered entities with high privileges the Normal World has no inherent mechanisms, not even DACR or XPUs, to protect against unauthorized memory accesses and manipulations from the Secure World. Therefore, it is trivial gaining access to the NW kernel for an attacker in case a TEE becomes compromised, even if no vulnerabilities were present in it.

#### 3. Taxonomy of attacks

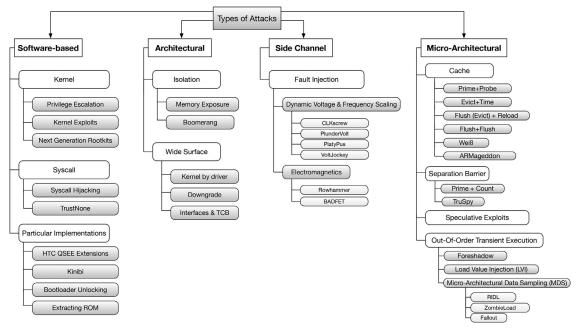

Although TEE has been designed to provide advanced means of secure code execution that traditional operating systems do not implement, they can still be attacked. Here we describe the taxonomy of attacks that will be used throughout the rest of the article.

Oualcomm Product Security. Retrieved from: https://www.qualcomm.com/company/product-security.

Fig. 5. Taxonomy of Attacks to TEE Implementations.

In addition, Fig. 5 provides a summary of every specific attack for each category.

- **Software-based attacks** (Section 4) are dedicated to exploit different elements of software stack, including operating system and the applications running on it.

- Architectural attacks (Section 5) exploit fundamental design flaws in the hardware architecture of the system, rather than software bugs.

- **Side-Channel attacks** (Section 6) are focused on the transmission of data between the Normal and Secure Worlds by modulating the behaviour of some system elements, such as execution times or power consumption.

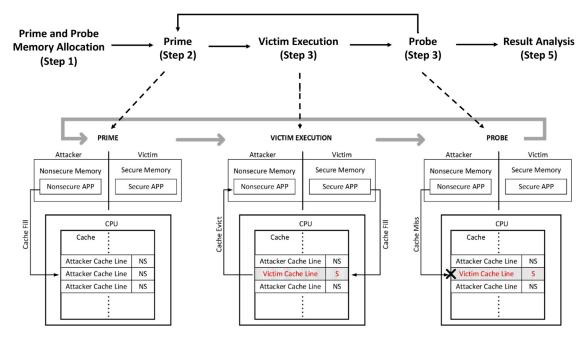

- **Micro-architectural attacks** (Section 7) are a particular type of attack that focuses on micro architecture elements such as exploiting the cache or Branch Target Buffer (BTB).

# 4. Software-based attacks

Programming errors cause functional inconsistencies, which can lead to bugs in the memory protection mechanisms, in the security mechanisms themselves, or in peripherals configuration. These bugs can appear randomly during the system execution, either during its validation with the trusted kernel, the secure monitor, the boot loader, or the applications themselves. Such bugs can be exploited through various means (e.g. parameter validation, buffer overflows) for various purposes – from revealing sensitive information to exploiting the kernel. In this section, the most representative TEE vulnerabilities caused by implementation bugs are described. Since each implementation has particularities in its architecture, which directly affect the way Trusted Applications (TAs) interact, we describe some of the most relevant cases exemplified in concrete implementations.

#### 4.1. Kernel attacks

This section describes direct attacks on the system kernel. This includes privilege escalation attacks, kernel exploits and a new generation of rootkits.

#### 4.1.1. Trustzone privilege escalation

Qualcomm's implementation, known as QSEE, is used in several smartphones – such as Pixel, LG, Xiaomi, Sony, HTC, One-Plus, and Samsung, among other devices. Due to its importance, there are various software-based attacks that specifically targets the Qualcomm implementation. One of such attacks focuses on accessing the protected memory of QSEE through escalation of privileges (Beniamini (2015b), Beniamini, Beniamini, Beniamini (2016a)).

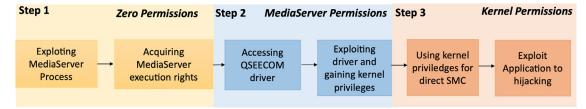

Fig. 6 shows the first three-stepped (Beniamini, 2015b) privilege escalation attack. Firstly, the attacker exploits a vulnerable implementation of the MediaServer Android application. This runs in the NW with zero permissions. Still, MediaServer was granted privilege for accessing the QSEECOM driver for communications with the TEE and therefore with the WineDive TA. Subsequently, the attacker could exploit a vulnerability in the QSEECOM driver and gain control of the kernel through the MediaServer. We highlight that this driver runs in NW context. Henceforth, the attacker with kernel privileges in the NW can make direct SMC calls to the SW. As a consequence, the attacker can manage to execute the code of his choice in the context of a TA. Moreover, since by making use of the SMC syscalls the privileged kernel applications have direct access to the TEE, the attacker can now execute various privilege escalation attacks to run shellcode within the TrustZone kernel.

Now, we will explain what additional steps need to be executed once an attacker gains control of QSEECOM. At this point, the attacker can execute SCM calls to write a zero DWORD in any specific memory address, in an operation known as 'zero-write primitive'. This can be used to disable the mechanism used for checking bounds on all memory addresses passed to the SW. Once this operation is disabled, the attacker can exploit other SCM calls creating different primitives. For example, once the control mechanisms are invalidated, the attacker can use the SMC calls to transform what was a 'zero-w primitive' to an arbitrary 'w-r primitive'. Once the attacker has achieved write permissions, he still has to identify those memory regions where to host his own shellcode, so as to bypass the TZ kernel pages protection mechanism. Since privileged kernel applications have direct TEE access, making use of SMC syscalls enables an important attack vector that may result in privilege escalation attacks.

Fig. 6. Three Stepped Privilege Escalation Attack.

The Domain Access Control Register (DACR) register from ARM MMU is responsible for protecting the TrustZone memory by controlling accesses to it. However, by making use of the arbitrary write primitives already described, it is possible to modify the value of the DACR and thus enable reading and writing the memory regions controlled by the mechanism. By doing so, the attacker can now insert his shellcode in memory areas reserved for execution within the kernel. Moreover, since these areas are never used by the kernel, any modification in them goes unnoticed.

# 4.1.2. Kernel exploit in TrustZone

This exploit describes how it is possible to take control of the operating system kernel through a series of chained exploits. This opens the door for the attacker to gain privileges to the TrustZone kernel. An example of this exploit is provided by Beniamini et al. (Beniamini,Beniamini), which describes how a series of chained exploits provide an alternative way to the previous attack. These chain of exploits take advantage of buffer overflows and vulnerable syscalls to ultimately execute arbitrary code with TrustZone kernel privileges.

The attack starts once the attacker has gained control of the QSEECOM driver, located in the NW. Now, the trusted Widevine application (located on the SW) can be exploited by causing buffer overflows, using a disused function called *PRDiagVerifyProvisioning()*. Once the buffer overflow is achieved, any code within the context of the trusted application can be executed. Still, although the attacker can make use of a Return-Oriented Programming (ROP) chain to execute his code, the application's executable code fragments are inserted as read-only. For this reason, the code execution must be split into two parts, where any part of code that does not require QSEE privileges will have to be executed within the Normal World.

At this point, access to the TEE is allowed indirectly through the use of certain (privileged) applications as intermediaries – and these, in turn, can then establish communication with the TEE through the driver. Even so, the attacker is restricted to running code in the QSEE user space, since he is not yet granted TZ kernel privileges. However, the attacker can exploit vulnerabilities in syscalls API provided by the TZ kernel.

The SVC instruction allows applications to call the syscalls of the TZ. This instruction is handled using the Vector Base Address Register (VBAR). Whenever a syscall is performed, control of the code and the execution flow passes to the NW kernel. However, the TZ only performs very basic validity checks on the provided input buffers: all arguments provided in legitimate application syscalls are accepted as valid. Therefore, once the attacker has identified a vulnerable syscall that allows him to overwrite any syscall handling function pointer, he can use the WideVine TAs to exploit the TZ kernel and modify the syscall handling functions. All that remains to be done is to identify a suitable memory area for inserting the shellcode. Despite of TA code segments can be considered write-protected due to the DACR mechanism, but in fact these segments are still susceptible to be overwritten with the described syscall bug.

Thereafter, as a consequence of disabling the DACR mechanism, the attacker can insert his shellcode anywhere in the application code. Likewise, he may also use mutated syscall control functions to execute his shellcode within the context of the TZ kernel and execute any arbitrary code. Note that classical security measures such as ASLR<sup>8</sup> could prevent common code execution and privilege escalation attacks, but they are not implemented in this context.

Precisely, Project Zero (Beniamini, 2017) provided an analysis on the implementation of such security measures in TEEs. They conclude that Qualcomm and Kinibi, the leading exponents of TEE implementations, only implement very few security mechanisms. In the case of Kinibi, it does not offer any type of ASLR mechanisms, forcing all applications to be loaded at a fixed memory address. On the other hand, Qualcomm's TEEs only offer a weak implementation of ASLR. Therefore, the security boundary between the TZ kernel and applications is very fragile, at least in concrete implementations like QSEE. In fact, when the attacker manages to enter the Secure World and takes over an application, the communication channel between TZ kernel and application is constructed in such a way that no input validation mechanism is implemented, and it is trivial for the attacker to compromise the kernel.

#### 4.1.3. Next generation rootkits

A series of rootkits considered to be new generation rootkits are included in this section, as they take advantage of several of the weaknesses already described and even others yet to be described related to architecture, side-channel or micro-architecture to explore weaknesses in the system.

Roth (2013) shows weaknesses in TEE combined with a specific architecture. They also describe how these weaknesses allow the development of rootkits such that they can control the system in a way that goes unnoticed. Since the SW has privileged access to the memory, it also has the ability to modify the NW kernel structures. Moreover, it can also block the NW from accessing its own memory. In particular, what Roth provided was several mechanisms to hide the visibility of the code running in the SW, thus complicating detection. Some of these rootkits exploit flaws in the TEE architecture itself to exploit vulnerabilities as described in Section 5, but these rootkits are software and although they also make use of attacks from other categories, they are eminently software for the most part and are therefore included here.

# 4.2. Attacks using system calls

This section includes attacks that make use of the set of system calls. Particular attacks such as TrustNone or hijacking attacks are included.

#### 4.2.1. Syscall hijacking

Certain attacks focus on executing various syscall hijackings in the context of the TEE in order to gain access to protected information. Along these lines, Beniamini (2016a) describe an attack that

<sup>8</sup> Address space layout randomization (ASLR) is a computer security technique used for preventing memory corruption vulnerabilities exploitation.

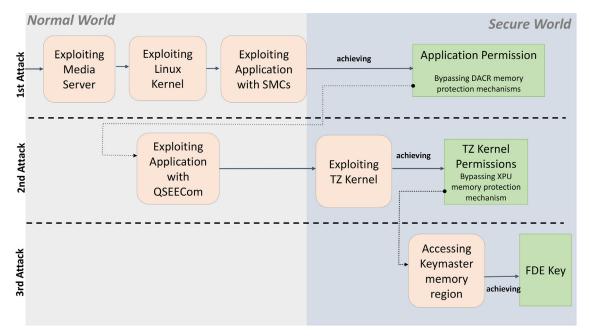

Fig. 7. Three attacks Overview.

can extract any key residing in TEE, as with the full disk encryption (FDE) key. This allows the attacker who successfully perpetrates the attack to decrypt any encrypted disk on the android device. This attack makes use of the different exploits described in Sections 4.1.1 and 4.1.2. For the sake of clarity, an overview of such attacks, including a description of how they are chained together, is shown in Fig. 7.

It essentially chains the previously mentioned exploits up to the point where the attacker has gained control of the QSEECOM driver and has exploited the vulnerable WideVine TA. However, because of the aforementioned XPU protection, QSEE applications do not have access to the memory of other QSEE applications. In particular, the Widevine TA cannot access the Keymaster memory. Still, every QSEE application has access to TZ kernel code segments as long as they are executed in the context of the kernel. The Widevine TA can execute the shellcode and thus access the Keymaster memory once the shellcode is hosted in the TZ Kernel. Therefore, the ultimate goal of the attacker is to insert the shellcode within the TZ Kernel and execute it through the Widevine TA. The shellcode will then access the Keymaster memory and extract the FDE Key.

In order to succeed in inserting the shellcode in the TZ kernel code segments, it is necessary to bypass various security mechanisms. The first mechanism to bypass is the DACR memory protection mechanism. The MMU manages access to any memory region, using bits of the DACR register. However, there is a piece of code inside the TZ core that can change the value of DACR, known as the DACR modifying gadget. If the attacker calls the DACR modifying gadget to set all bits to 1, then all memory regions are then enabled and available to perform read and write operations on them. The first goal of the attacker is to execute this DACR modifying gadget.

In order to execute this gadget, the attacker can take advantage of the design of the system call table. System calls are used indirectly using a system call table. Although this table cannot be changed, as it is protected by the memory protection unit (XPU) pointers, the reference to this table is not protected: it must reside in a modifiable memory region, because it is only filled at runtime. Because of this, the attacker can execute a sycall hijacking attack: the attacker stores in memory a fake system table with one system

call pointing to the DACR modifying gadget, and then modify the reference to the system call table so it points to the malicious one. This way, once the (modified) syscall is called, the DACR modifier gadget will be invoked instead – modifying the DACR register to allow write and read access.

The second security mechanism that needs to be bypassed is the memory protection unit (XPU), which prevents access to protected areas from unprivileged code. The issue here is that the attacker can execute code in the kernel context, yet the source of the code is in the trusted WideVine application – and is therefore considered unprivileged. The attacker then must find a way to insert the malicious code in the TZ kernel and to invoke it.

The attacker first needs to implements a script in order to identify unprotected code regions in the TrustZone kernel. This allows finding a "cave" to host the final shellcode of the exploit, which will be considered as priviledge code and will bypass the XPU protection mechanism. Once the script successfully finds a "cave" and the shellcode that extracts the encryption key from the memory disk is inserted, a final step remains: how to execute such shellcode. In order to do so, another system call hijacking is needed. For example, the attacker can overwrite the qsee-hmac() system call. As a result, when the qsee-hmac() is called from the malicious QSEE application, instead of the intended function the shellcode will be executed. This allows the FDE key to be extracted from the KeyMaster application and then written to the shared buffer.

The cause of this attack is that disk encryption is not implemented with a hardware-based key. The key is generated by software and stored inside the TZ kernel memory. Since the key resides within the software, once the TZ kernel is exposed, it can be easily extracted. Therefore, the disk encryption system offered by Android becomes resistant to attacks of different kinds such as those of the TZ kernel security or TA's own keymaster. Any flaw in either of them can potentially leak the FDE master key.

In addition to the ability of applications to map physical memory, there is another attack gap arising from TEE's debugging mechanisms. What privilege escalation attacks are and how they work has already been described in Section 4.1.1. Making use of this type of attack, Shen (2015) implements an attack on Huawei's TEE. It exploits a syscall that allows any application to perform a stack dump in a memory area belonging to the NW. This becomes

Fig. 8. Kinibi Architecture.

the attacker aware of the physical address space of the GlobalTask to have enough information to successfully implement the attack.

#### 4.2.2. Trustnone

Communication with the TZ kernel is facilitated through the SMC instruction, as aforementioned. This allows the NW to use system calls that are exported by the TZ kernel, for which an API is provided in the Android/Linux kernel.

XPU units protect those on-chip and off-chip memory regions that contain the TZ kernel. These are configured by the first boot loaders. This allows only certain runtime environments to access certain memory areas.

Beaupre (2015) describes that a number of TZ vulnerabilities are related to system calls. With special emphasis on those that do not implement any validation, or do not do it properly. More specifically, in the user input, at this point the attacker could safely write as many zeros as desired in a memory area, thus bypassing the implemented security mechanisms obtaining read and write permissions in the TZ kernel context.

The attack is particularly relevant because it affects all devices using the Snapdragon 805 SoC and thus the QSEE. In his experiment, Beaupre used the exploit to unlock the bootloader of a Motorola Snapdragon 805<sup>9</sup>

# 4.2.3. Attacks on HTC QSEE extensions

Beyond the vulnerabilities that can be found on QSEE, there are also vulnerabilities that affect certain QSEE extensions from specific manufacturers. For example, in Keltner and Holmes (2014), Keltner et al. describe the implementation of a new attack against a version of Qualcomm's QSEE used and extended by HTC. To create this attack, they reverse-engineered that specific implementation/version of QSEE, which proved highly successful in finding a number of vulnerabilities in the code added by the HTC extensions.

Examples of such vulnerabilities include i) flaws in the zero-write primitive in certain address range allowing to circumvent all memory operations security checks, and ii) flaws in the "tzbsp\_oem\_memcpy" function, which give the attacker full control of all the memory. As a consequence of all the weaknesses, it is easier for the attacker to securely extract data and modify validation mechanisms in memory regions.

# 4.2.4. Implementation bugs

The previous sections have focused on the QSEE TEE by Qualcomm. Yet this is not the only vulnerable implementation of the standard: other vulnerabilties have also appeared in other implementations of the TrustZone technology, such as Kinibi (Lapid and Wool, 2018) from Trustonic.

One important work in this area is proposed by Komaromy (2018) that described certain important vulnerabilities affecting the Trustonic implementation. These six vulnerabilities were caused by software bugs, and most of them are located in components that manage inter-realms communications.

Before describing these vulnerabilities, it is important to provide a very brief introduction on the Trustonic architecture. Trustonic (cf. Fig. 8)includes an application connector or gate-

keeper known as TLC (trustlet connector) that enables communication to pass through to the Kinibi device. An interface is offered to NW by TLC that can be accessed through UNIX domain sockets. These domain sockets make use of MAC/DACs schemes for access control and only certain applications, such as *tlc\_server*, have access to them. In addition, sanity checks are performed on TEE requests, and are further protected through SELinux.

Komaromy (2018) found a way to circumvent this access control by disassembling the *tlc\_driver* binary. It was found that although almost all commands implemented a process for checking the caller's permissions, there was one command that, for some reason, did not have this security check implemented. This vulnerability, *Vuln 0*, allowed an arbitrary user-space application to make use of the handler and initiate a session to a TA and subsequently send any commands at will to it.

One of such trusted applications (TA or trustlet) is ESECOMM, which is used for secure payment transactions. ESECOMM implements the "SCP03 Global Platform Secure Channel Protocol", where messages are sent encoded in TLV (Type-Length-Value) format via APDUs (Application Protocol Data Units). The trusted application performs certain parsing ckecks on the TLV-enconded messages but does not control whether the maximum number of TLVs to store for each structure is exceeded. This may result in overflow (Vuln 1) attacks, which opens up the range of possible attacks since these structures are allocated on both the heap and the stack. In addition, the TLV parser does not properly check the input buffer (allocating TLVs) length – the only check performed is whether the offset remains unchanged until the end of the buffer, it does not check that it is less than it. Therefore, this allows an attacker to trivially read out of bounds (Vuln 2).

However, these are not the only vulnerabilities that affect the ESECOMM trustlet. There is another stack buffer overflow in the "parse\_ca\_cert()" function. Again, no check is made on the length of the TLV input value, so it is possible that another buffer overflow may occur. Although the size of TLVs is restricted to 0x400 bytes, since the size of the input buffer is limited to 32 bytes, the proposed restriction is not sufficient to prevent the attack (Vuln 3).

There is another function, "parse\_scp\_param()", with a similar vulnerability. This function is used to parse the Diffie-Hellman Diffie and Hellman (1976) parameters used for establishing a secure channel between Kinibi and the secure element. As in the previous case, the function parses and checks most of the parameters but there is one parameter that is not fully checked, thus enabling another overflow (Vuln 4) attack.

Finally, the fifth vulnerability (*Vuln 5*) is a memory corruption vulnerability that requires the user to have root privileges. The main problem lies in the common buffer shared by that both worlds, NW and SW. In this buffer, known as TCI, there is a flaw in the way memory offsets are specified. In particular, within the buffer there is a file (*envelope\_len*) with the offset where the response begins. The tlc\_driver is in charge of setting this field, but any other trusted application can also do it. As a result, if an attacker is able to become root, he would be able to arbitrarily modify this field and thus specify whatever write offset he wishes, even beyond the buffer bounds.

While we have focused on vulnerabilities that affect the Kibini implementation, that does not mean that there are no flaws in other TrustZone implementations. For example, in Keltner and

<sup>&</sup>lt;sup>9</sup> https://www.qualcomm.com/products/snapdragon-processors-805.

Holmes (2014), the authors describe the procedure to read and write operations on arbitrary memory locations within the SW using the failed memory validation mechanism. Similarly, Rosenberg (2014) observed a faulty SMC memory check mechanism. This flaw enables an attacker with kernel privileges to write into the SW.

#### 4.2.5. Unlocking bootloader attacks

There are other TrustZone attacks that target the bootloader of smartphones, such as the attacks described by Rosenberg (2013, 2014). In the first paper, Rosenberg describes a write vulnerability in Motorola smartphones. This vulnerability affected a specific SMC call whose role was to allow the kernel in the NW to obtain values stored on the memory side of the safe world. However, an attacker can abuse this SMC call to overwrite the memory in the secure region – in particular, the flag responsible for granting the TrustZone kernel permission to blow Qfuses. As a result, the attacker can blow Qfuses through another SMC call, in order to indicate that the bootloader is unlocked. This way, an unsigned image (e.g. a tampered Android firmware) can be loaded.

In the second paper, Rosenberg (2014) identifies a new vulnerable SMC function. The function, known as *qsee\_is\_ns\_memory()*, checks whether a certain memory range belongs to the SW. This function involves an uncontrolled primitive write based on an overflow. This vulnerability enables a chain of attacks that gives the attacker the possibility of circumventing all validation checks and execute any code in safe memory region, unlocking the bootloader in the process.

# 4.2.6. ROM Extraction attack

There are other attacks, such as Basse (2016) by Basse et al., whose goal is to bypass the TrustZone authentication mechanisms to extract the boot image (BootROM) from a device. In ARM devices, an UART interface is available in the device to give access to a root shell and a high-level debug message interface. Still, the BootROM image is stored in a secure memory area within the SoC to prevent unauthorised access or changes. To bypass the security measure two conditions must be met: i) the MMU tables must be extended to include the BootROM address (thus allowing access to this partition), and ii) the user needs kernel privileges.

Although an attacker can exploit existing overflow errors in the SMC interface to gain kernel privileges, the access to the memory is limited due to the authentication routine that protects the MMU images. However, in some cases, this authentication routine is a mere hash function. Therefore, an attacker can update the MMU table to include the BootROM, recalculate the hash of the MMU table, and write both values in the device. A custom SMC can then be executed, which will access the BootROM partition through the tampered MMU table.

# 5. Architectural attacks

This section presents the main security issues arising from the architecture of today's TEE systems. We distinguish between attacks made possible by the elements of the architecture dedicated to the isolation between worlds (SW vs NW) and attacks on memory protection mechanisms.

# 5.1. Isolation focused attacks

Attacks on inter-world isolation include (a) memory exposure due to physical memory mapping in the NW by applications, and (b) information leakage due to TEE debugging mechanisms.

#### 5.1.1. Memory exposure

Certain TAs require an efficient shared memory mechanism with the ability to exchange large volumes of data between worlds, which has led to security holes in some TEE implementations.

Beniamini Beniamini (2016b) describes how an attacker, starting with only TA privileges running in the NW, can get full control of the kernel, which is due to the fact that Qualcomm's TEE implementation allows an arbitrary application to allocate an arbitrary area of the Normal World. For this, it is only necessary to use a call to the SW, which in turn allows the attacker to take control of the operating system. This would enable him to sweep through all the physical addresses of the kernel, manipulate it and introduce backdoors

Fortunately this is not the case for all implementations. In the case of Trustonic TEE, TAs cannot read from or write to physical memory.

#### 5.1.2. BOOMERANG attack

Boomerang attacks Wagner (1999) exploit flaws that appear in the design of the communication between realms. This type of attack is made possible by the fact that the trusted OS has no restrictions on the memory addresses it can access and the normal OS has no way of checking if the entity performing this action is entitled to do so. The attack starts with an application or user in the NW passing an unauthorized memory address to a SW call. If the address is not filtered out due to the lack of standard memory sanitation mechanisms, the attacker could read and/or write that memory, as detailed in Section 7.1.

Fig. 9 shows an overview of the attack. The attacker's goal is to send a privileged address to the application (4). For this purpose, and in order to circumvent the sanitation process, a filled data structure is transferred – which among other things contains an address pointer without annotating it. There are three possible ways to transfer the data to the existing mode: (1a) by using the Daemon TEE in charge of pointer sanitation with background execution, (1b) by taking advantage of an API that is used by the application, and (1c) by using a library for the aforementioned API. The NW OS kernel makes a call to the SMC with the purpose of switching worlds and transferring the filled data structure to the SW (2). Once the data structure is in the SW OS, a check is made to see if the pointers actually point to memory areas from the SW. As the pointer comes from the NW, it passes the test and the trusted OS passes the structure to the TA (3) without any further checks.

Based on how an attacker bypasses pointer sanitation, Machiry et al. (2017) successfully attacked a wide variety of TEE architectures. Using a static analysis tool, they were able to perform analysis of several TEE implementations (QSEE, Kinibi, OP-TEE (Brand), SierraTEE (SierraWare), and Huawei) and applications on them, searching for BOOMERANG vulnerabilities. The results of the study revealed several vulnerabilities in the analyzed platforms, which affected a very high number of mobile devices. This work has enabled TEE vendors to implement specific fixes in their environments.

# 5.2. TEE Wide attack surface

Attacks to memory protection mechanisms include certain bugs appearing in software drivers (executed in kernel space), others appearing in the interfaces shared among different TEE components and broad interfaces.

# 5.2.1. Kernel contains driver execution

Most systems require software drivers to communicate with specific hardware. Some TEE drivers are meant to interact with devices that handle sensitive (e.g. a biometric sensor) and for that reason they are executed in the TEE kernel. Therefore, an attacker

Fig. 9. An attacker bypasses pointer sanitation by hiding it inside the structure to send to applications.

could exploit any error in these drivers in order to access the privileged area of the system. In fact, some implementations like OP-TEE Brand and Snapdragon (Rosenberg, 2014) allow the execution of all the code labelled as privileged within the kernel.

# 5.2.2. Downgrade attack

Trusted applications are signed using the TEE trusted public key. If the application passes the verification, the system will accept it and execute it. This is exploited by downgrade attacks, which consist of loading old buggy binaries to take control of the system. Chen et al. (2017) demonstrated the effectiveness of this kind of attack.

Nowadays, in order to prevent such attacks, the majority of TEEs implementations include some kind of mechanism to control the application versioning. However, Beniamini (2017) analysed a number of applications and their respective updates and realized that all shared the same version number.

Application developers are therefore urged to make use of the version control mechanisms provided by the TEE vendors. This shows that even when protection mechanisms are in place it is important to make use of them or they are rendered useless thus opening the door to attacks.

# 5.2.3. Broad interfaces to attack

Opening secure system has always been tricky and dangerous. In order to extend functionalities the number of interfaces offered by TEE is growing and this has led to the development of several exploits. For example, the exploit on the TZ linux driver (Beniamini, 2015a) in Android. Trusted applications are also being provided with more functionality, which is also sensitive from a security point of view.

TEEs should allow developers to minimise the Trusted Computing Base (TCB) of their applications to maintain a proper security/efficiency balance: the larger the size of the TCB, the more error-prone implementations are (Cerdeira et al., 2020). It is worth noting that the size of the TCB varies considerably for TEE each implementation, ranging from 97KB for Tegra's TEE to 1.62MB for Qualcomm's.

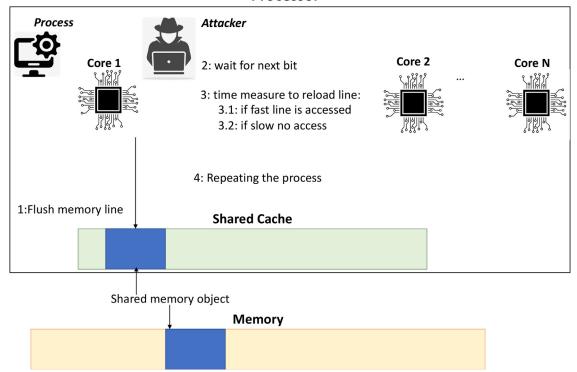

#### 6. Side-Channel Attacks

As mentioned above, memory protection mechanisms in TEE implementations are rather weak or lacking. In this section we show how exploiting these mechanisms lead to side-channel attacks (SCA). An SCA is an attack that exploits certain types of information such as power consumption data to leak information about cryptographic material and operations.

Fault-injection is a particular kind of side-channel attack consisting on inducing physical- or software-based faults (also referred to as glitches) in a computation to expose secret information. Due to their relevance, we focus on this type of attacks. This type of attacks include the application of high voltages, temperatures or electromagnetic (EM) pulses in order to expose electronic components to unexpected conditions. Electromagnetic fault injection (EMFI) attacks Maistri et al. (2014) are probably the most relevant and difficult to protect from. These attacks have provided very successful results when implemented on a huge number of commercially available integrated circuits.

Some of the most relevant fault-injection attacks are known as Dynamic Voltage and Frequency Scaling (DVFS), which allow the software to regulate device voltage and frequency based of each CPU execution thread. This makes it possible to modify and monitor the power consumed since this value is directly related to both factors (frequency and operating voltage). Some of them, namely CLKscrew Tang et al. (2017), Plunder-Volt Murdock et al. (2020b), Platypus attack Lipp et al. (2021) and VoltJockey Qiu et al. (2019a) are based on producing dynamic voltage and frequency scaling, where power traces can be collected by software and there is no need to physically access the device itself. Additionally, Rowhammer Lipp (2016) and BADFET Cui and Housley (2017) are attacks based on the application of electromagnetic pulses.

# 6.1. CLKscrew

CLKscrew takes advantage of a feature available in modern devices that enables software control of both CPU voltage and frequency for the primary purpose of power administration.

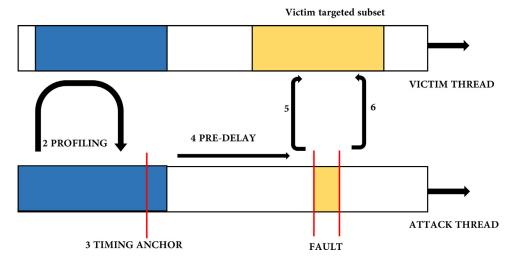

Fig. 10. CLKscrew fault injection Attack.

Tang et al. (2017) show a successful implementation of the attack on an ARM device, namely the Nexus 6 smartphone. This attack consists of inducing failures in certain operations by causing calculation errors in the CPU, allowing the attacker to obtain essential information to deduce secret keys from an ARM TrustZone.

To cause erroneous behaviour, the attacker can overclock and undervolt the CPU, thereby exceeding the CPU fault induction boundaries. There are no protection mechanisms to prevent the CPU from being able to operate at faulty frequency and voltage combinations. Also, since hardware regulators <sup>10</sup> have their operating range precisely at the TEE separation, this opens the possibility that the attack can occur even in the same SW execution.

Once frequency-voltage combinations of faulty behaviour have been identified, the attacker makes use of a manipulated kernel driver that manages to link the victim's thread to a particular kind of kernel, leaving the rest of kernels to other applications. This avoids the threat of possible collateral damage during the attack. In addition, interrupts are disabled during fault injection, which allows circumventing any possible context switching.

A representation of the attack is depicted in Figure 10. The attack requires some preparation: it starts with clearing out any cache residue, since in the following phases of the attack a cachebased profile is used to signal the start of the victim's execution (step 1). Then, the attacker monitors the victim's code execution by inspecting certain execution points, called "Timing Anchor" point, especially in the instant prior to the execution of the target code where the fault is to be injected (steps 2-3). There are some cases where the accuracy of the Timing Anchor is not good enough, thus it is necessary to achieve a more precise synchronization of the attack. To fine-tune the accuracy, the attacking thread remains in a loop for a period of time, after which it will proceed to the next step of the process (step 4). Note that a distinguishing feature of this attack is that the frequency of the victim's CPU kernel undergoes changes while the attack is taking place, raising the frequency value to a specified one and over a specified period - and then restoring normal conditions (steps 5-6).

Using this attack technique, it was possible to unveil the secret key of a previously manipulated implementation of AES executed in the Secure World. The implementation consisted of a simple decryption tool that received encrypted messages as input and returned the plaintext, decrypted with a stored secret key. The attacker was able to unveil the AES secret key by inducing various glitches during the AES decryption phase and applying differential fault analysis (DFA) attack.

The authors also showed a second type of attacks on TZ with CLKscrew, which they call *self-signed application loading*. In this case, CLKscrew can be used to modify the RSA signature chain of firmware images in TZ, which is the method used for verifying their authenticity. Firmware images to be updated contain the updated code, a signature of the firmware's hash to maintain its integrity, and a certificate chain. During the upgrade process, a verification of the signature is performed on the hash of the new firmware to be uploaded, together with a secret key linked to the hardware (this key is stored in the Secure World). Using CLKscrew, the authors are able to crack the signature process to force it to produce a hash that is identical to the hash of a different firmware. Consequently, the verification mechanism accepts to install an illegitimate firmware as if it were correctly signed by a trusted entity.

#### 6.2. PlunderVolt

Plundervolt Murdock et al. (2020b) relies on the inducing changes to the voltage received by the processor, causing the program to change its intended execution path. Pundervolt exploits the lack of a stable power supply voltage.

Plundervolt circumvents the protection limits of the TEE memory encryption engine by abusing an undocumented voltage scaling interface, which allows privileged software adversaries to lower the tension and cause predictable failures in the SW. With this technique, the theft of secrets is achieved, even in the presence of memory encryption technology.

For instance, Plundervolt can break the integrity and (indirectly) the confidentiality of Intel SGX Murdock et al. (2020a). Indeed, as a consequence of Plundervolt it is possible to break the processorüs instruction set specification, making it possible to successfully attack bug-free code, tested code and even formally verified code. Unlike other Intel SGX attacks, which abused architectural design flaws to break the confidentiality of enclave secrets, the authors demonstrated that even the integrity of seemingly secure enclave computations can no longer be trusted. The authors in addition to succeeding in breaking cryptographic code show how Plundervolt can be used to induce memory safety vulnerabilities into bug-free code.

$<sup>^{10}</sup>$  Hardware can include voltage/frequency regulators, which contain a phase-locked loop (PLL) circuit that generates a synchronous and adjustable clock signal for the digital components.

#### 6.3. Platypus Attack

Platypus Lipp et al. (2021) is based on exploiting the mechanism of accessing the interface of Intel's RAPL - Running Average Power Limit, which reveals information about power consumption. The weakness lies in that any user of the system can access this interface.

Platypus shows that by performing a statistical study with a certain number of evaluated data, it is possible to appreciate and identify variations in energy consumption. By assigning different Hamming weights to what is loaded into memory, different code instructions can be identified. This makes it possible to monitor the control flow of applications, which is very valuable to a potential attacker.

Using Platypus, an attacker has also the ability to deduce sensitive information such as secret keys. The authors show how a potential attacker, who starts from an unprivileged state, is capable of obtaining AES new instructions (AES-NI) keys from Intel SGX and the Linux kernel, infer secret instruction streams, break the randomisation of the kernel address space layout (KASLR) and finally achieve the establishment of a time-independent covert channel.

#### 6.4. VoltJockey

VoltJockey Qiu et al. (2019a) is an attack based on dynamic voltage and frequency scaling (DVFS). This attack differs from others (e.g. CLKscrew) in that it performs manipulations on voltages instead of frequencies. This allows the generation of failures in the target hardware. VoltJockey is notable for being more stealthy and therefore more difficult to avoid than similar attacks such as CLKscrew. Some authors Qiu et al. (2019a); Qui et al. (2020) have shown how TrustZone's AES key and RSA-based authentication can be cracked on an Android smartphone using VoltJockey. This is one of the most effective attacks for obtaining protected TrustZone credentials.

VoltJockey is an attack on TrustZone based on hardware flaws using software-controlled voltage manipulation. It exploits the DVFS voltage management vulnerability. In Qiu et al. (2019a); Qui et al. (2020) the authors implement VoltJockey on an ARM-based Krait multicore processor, whose core frequencies can be different but the processor voltage is controlled by a shared hardware regulator. The Trust-Zone protected AES key is achieved and thus guide the RSA-based signature verification to obtain the target plaintexts. An implementation of VoltJockey was used to break Intel SGX in Qiu et al. (2019b) and in an advance scaling based fault injection Oiu et al. (2020).

#### 6.5. Rowhammer

The Rowhammer attack Lipp (2016) exploits the particular design of some modern DRAM memory in which memory cells are getting closer and closer. This complicates isolation and makes DRAM cell capacitors sensitive to electrical interference thus potentially leading to memory corruption. As such, the repeated access to a row of memory can cause bit flipping (shifts from 0 to 1 and vice versa) in adjacent rows.

Consequently, Rowhammer takes advantage of this isolation problem to affect the RAM rows storing TrustZone data, even bypassing the NS bit protection mechanism. The authors of the attack, from Carnegie Mellon University and Intel, tested this phenomenon on Intel and AMD systems using a program that generates multiple accesses to DRAM memory. They managed to cause errors in most of the DRAM modules tested (110 out of 129) from three major manufacturers.

#### 6.6. BADFET

In recent years, electromagnetic fault injection (EMFI) attacks are becoming a major threat. This is as a consequence of the massive increase in CPU speed and the reduction of the size of the components, which hinders other types of injection attacks.

BADFET Cui and Housley (2017) is based on *second-order* EMFI attacks, which do not target the CPU but other components of the system. In fact, this attack can be applied to any arbitrary component (such as memory, buses, controllers, etc.) that the processor makes use of during sensitive operations. This approach can significantly reduce the temporal and spatial resolution requirements of the hardware needed for EMFI injection.